# **Design and Development of DC to AC Inverter**

by

# Nur Fairuz Binti Mohamed Yusof

A Dissertation Submitted For Partial Fulfillment of The Requirement For The Degree of Master of Science

July 2012

### ACKNOWLEDGEMENT

Thanks to Allah for giving me this opportunity, strength and patience to complete my dissertation, finally, after all of the challenges and difficulties.

First and foremost, I would like to express my greatest gratitude to Dr. Shahid Iqbal, who have guided, encouraging and helped me a lot throughout this dissertation process.

This appreciation is also dedicated to all my friends who help me in this project. Especially to whom is responsible sharing knowledge with me Mrs.Chanuri, Mr.Lee and Mr.Faizal.

Finally, I dedicate my warmest and deepest appreciation to both of my parents, Mr. Mohamed Yusof and Mrs. Norliza Omar and my beloved husband, Mr.Ahmad Mohamad Omar and also my siblings for their understanding, patience, encouragement and support during the completion of this dissertation and never stop inspiring me.

# TABLE OF CONTENTS

| Ackno   | wledgementii         |

|---------|----------------------|

|         | of Contentsiii       |

| List of | Tables               |

| List of | Figures              |

| List of | Symbolsxi            |

| List of | Abbreviation         |

| Abstra  | ctxiii               |

| Abstra  | Tables               |

| СНАР    | TER 1 – INTRODUCTION |

| 1.00    | Background1          |

| 1.1     | Problem Statement    |

| 1.2     | Objectives4          |

| 1.3     | Thesis Outline       |

# **CHAPTER 2 – LITERATURE REVIEW**

| 2.0        | Introdu | action                                                    |

|------------|---------|-----------------------------------------------------------|

| 2.1        | Single  | Phase Inverter Topology6                                  |

|            | 2.1.1   | Half Bridge Inverter7                                     |

|            | 2.1.2   | Full Bridge Inverter                                      |

| 2.2        | Sinuso  | Full Bridge Inverter                                      |

|            | 2.2.1   | SPWM Inverter – Bipolar Switching                         |

|            | 2.2.2   | SPWM Inverter – Unipolar Switching                        |

| 2.3        | Review  | w of Previous Single Phase Inverter with SPWM switching15 |

| 2.4        | Compo   | onent Description                                         |

|            | 2.4.1   | Power Switch                                              |

|            | 2.4.2   | LC Filter                                                 |

| $\bigcirc$ | 2.4.3   | Triangular Wave Generation                                |

|            | 2.4.4   | Sinusoidal Wave Generation                                |

| 2.5        | Summ    | ary25                                                     |

# **CHAPTER 3 – DESIGN AND IMPLEMENTATION**

| 3.0        | Introduction                                  | 26 |

|------------|-----------------------------------------------|----|

| 3.1        | Overall System Design                         | 28 |

| 3.2        | Description of Inverter Topology              | 28 |

| 3.3        | Selection of IGBT for the Power Circuit       | 31 |

| 3.4        | SPWM Switching Signal Generation Circuit      | 32 |

|            | 3.4.1 Triangular Wave Design                  | 33 |

|            | 3.4.2 Sinusoidal Wave Design                  | 36 |

| 3.5        | Gate Driver Circuit                           | 37 |

| 3.6        | Low Pass Filter                               | 38 |

| 3.7        | Simulation of Inverter Circuit                | 39 |

|            | 3.7.1 Simulation Using PSIM                   | 40 |

| $\bigcirc$ | 3.7.2 Simulation using Pspice                 | 41 |

| 3.8        | Hardware Implementation                       | 42 |

|            | 3.8.1 Testing on Breadboard                   | 43 |

|            | 3.8.2 PCB Layout drawing in OrCAD fabrication | 44 |

|            | 3.8.3 Experimental Setup                      | 47 |

# **CHAPTER 4 – RESULT AND DISCUSSION**

| 4.0        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.1        | PSIM Simulation Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 4.2        | PSpice Simulation Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 4.3        | Experimental Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 4.4        | Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| СНАІ       | Experimental Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|            | for the second |  |

| 5.0        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.1        | Future Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|            | emispro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| REFERENCES |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 4          | (h).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| APPE       | NDICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

# LIST OF TABLES

# Page

| Table 2.0 | Differential between IGBT and MOSFET                                                                                                          | 19 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 | Ratings and specifications of IGBT type IRGB4064DPbF                                                                                          | 31 |

| Table 3.2 | Ratings and specifications of op-amp type LM833                                                                                               | 33 |

| Table 3.3 | Equipments and measurement devices                                                                                                            | 47 |

| OTHIS     | Ratings and specifications of IGBT type IRGB4064DPbF<br>Ratings and specifications of op-amp type LM833<br>Equipments and measurement devices |    |

# LIST OF FIGURES

| Figure 2.1 | Half-bridge configuration                                | 7  |

|------------|----------------------------------------------------------|----|

| Figure 2.2 | Two-level output waveform of half-bridge configuration   | 8  |

| Figure 2.3 | Full-bridge configuration                                | 9  |

| Figure 2.4 | Two-level output waveform of full-bridge configuration   | 9  |

| Figure 2.5 | Three-level output waveform of full-bridge configuration | 10 |

| Figure 2.6 | SPWM with Bipolar voltage switching (a) Comparison       | 12 |

|            | between reference waveform and triangular waveform       |    |

|            | (b) Gating pulses for S1 and S4 (c) Gating pulses for    |    |

|            | S2 and S3 (d) Output waveform                            |    |

| Figure 2.7 | Harmonics Spectrum of Bipolar SPWM                       | 13 |

| Figure 2.8 | SPWM with Unipolar voltage switching (a) Comparison      | 14 |

|            | between reference waveform and triangular waveform       |    |

|            | (b) Gating pulses for S1 and S4 (c) Gating pulses for S2 |    |

|            | and S3 (d) Output waveform                               |    |

| Figure 2.9 | Harmonics Spectrum of Unipolar SPWM                      | 15 |

| Figure 2.10 | Design concept for a basic triangular-wave generator | 22 |

|-------------|------------------------------------------------------|----|

| Figure 2.11 | Phase-Shift Oscillator (Single Op Amp)               | 24 |

| Figure 2.12 | Output of the Phase-Shift Oscillator (Single Op Amp) | 25 |

| Figure 3.1  | Flowchart for the solar inverter project development | 27 |

| Figure 3.2  | Block Diagram of the hardware design                 | 28 |

| Figure 3.3  | Single phase inverter and its control strategy.      | 29 |

| Figure 3.4  | Steady state operation for positive half cycle       | 30 |

| Figure 3.5  | Steady state operation for negative half cycle       | 30 |

| Figure 3.6  | Structure of IGBT type IRGB4064DPbF.                 | 31 |

| Figure 3.7  | Structure of LM833                                   | 32 |

| Figure 3.8  | Triangular wave oscillator.                          | 33 |

| Figure 3.9  | Sinusoidal wave oscillator                           | 36 |

| Figure 3.10 | Connection of gate driver to IGBTs                   | 38 |

| Figure 3.11 | LC low pass filter                                   | 39 |

| Figure 3.12 | Schematic diagram using PSIM version 9.0             | 40 |

| Figure 3.13 | Complete single phase inverter in Pspice             | 42 |

| Figure3.14  | SPWM switching circuit testing on breadboard         | 43 |

| Figure 3.15 | Single phase inverter with gate driver circuit testing on breadboard | 43 |

|-------------|----------------------------------------------------------------------|----|

| Figure 3.16 | PCB layout SPWM switching scheme circuit                             | 45 |

| Figure 3.17 | PCB layout for phase inverter with LC filter and gate driver circuit | 45 |

| Figure 3.18 | The complete single phase inverter with SPWM switching scheme        | 46 |

| Figure 3.19 | Experimental equipment setup                                         | 47 |

| Figure 4.1  | Schematic diagram of single phase full bridge inverter               | 49 |

| Figure 4.2  | Sinusoidal wave setting in PSIM                                      | 49 |

| Figure 4.3  | Triangular wave setting in PSIM                                      | 50 |

| Figure 4.4  | Reference wave and Triangular wave from voltage source               | 50 |

|             | generator                                                            |    |

| Figure 4.5  | SPWM switching scheme                                                | 51 |

| Figure 4.6  | Single phase inverter output voltage before LC filter                | 52 |

| Figure 4.7  | Single phase inverter output with 165 $\Omega$ resistive load        | 52 |

| Figure 4.8  | Triangular wave from oscillator circuit                              | 54 |

| Figure 4.9  | Sinusoidal wave from oscillator circuit                              | 55 |

| Figure 4.10 | Reference wave and Triangular wave for Pspice simulation             | 55 |

| Figure 4.11 | SPWM switching drives the single phase inverter                      | 55 |

| Figure 4.12 | Single phase inverter output with $18\Omega$ resistive load  | 56 |

|-------------|--------------------------------------------------------------|----|

| Figure 4.13 | Triangular wave oscillator output                            | 58 |

| Figure 4.14 | Sinusoidal wave oscillator output                            | 58 |

| Figure 4.15 | Input of the comparator to produce SPWM                      | 59 |

| Figure 4.16 | SPWM switching scheme                                        | 59 |

| Figure 4.17 | Single phase inverter output before LC filter                | 60 |

| Figure 4.18 | Single phase inverter output with $165\Omega$ resistive load | 60 |

| Figure 4.19 | Single phase inverter output when capacitor $= 53$ nF        | 62 |

| Figure 4.20 | Single phase inverter output when capacitor $= 2uF$          | 62 |

| Figure 4.21 | Single phase inverter output when capacitor = 30uF           | 63 |

| Figure 4.22 | Single phase inverter output when capacitor $= 45 \text{uF}$ | 63 |

| Figure 4.19 | Single phase inverter output when capacitor 50uF             | 64 |

| S           |                                                              |    |

# LIST OF SYMBOLS

- Efficiency η

- Output Power Pout

- P<sub>in</sub> Input Power

- D Duty Cycle

- Output Voltage Vout

- $V_s$ Input Voltage

- Output Current Iout

- Input Current I<sub>in</sub>

- y original copyright Frequency modulation ratio  $\mathbf{m}_{f}$

- Modulation ratio ma

- Output Power othisitemis  $\mathbf{P}_{\text{out}}$

xii

## LIST OF ABREVIATIONS

- AC Alternative Current

- DC Direct Current

- Insulated Gate Bipolar Transistor IGBTs

- Metal Oxide Semiconductor Field Effect Transistor Maximum Power Point Tracking Printed Circuit Board Pulse Width Modulation Photovoltaic MOSFET

- MPPT

- PCB

- **PWM**

- PV

- Sinusoidal Pulse Width Modulation .ise W. othisitemis protection **SPWM**

### DESIGN AND DEVELOPMENT OF DC TO AC INVERTER

### ABSTRACT

This thesis describes the design and construction of a Single Phase Full Bridge Inverter with Sinusoidal Pulse Width Modulated (SPWM) switching scheme. The design of inverter consists of four parts which are control circuit, gate driver circuit, power circuit and LC filter. An analog type controller is used for generating the desired SPWM control signal. The analog controller consists of triangular wave generator and sine wave generator. Triangular wave is generated by using combination of Schmitt trigger and integrator that is able to produce 12Vpeak to peak at 2.326kHz frequency. While the sinusoidal wave oscillator circuit is made up of phase shift, voltage follow and buffer and it produces an output sine wave at a frequency of 54 Hz. In gate driver circuit, HCPL-3020 is employed to drive the SPWM signal to the power switching circuit. While for the power circuit, four IGBTs are used as power switching devices. The complete circuit is simulated in PSIM software using real values from hardware testing. The inverter circuit is also simulated using PSpice software to observe the overall performance of the circuit when supplied an input voltage of  $310V_{DC}$ . The simulation results confirm the good operation of the inverter circuit. Besides that, hardware prototype of inverter is also implemented and tested.

# REKABENTUK DAN PEMBANGUNAN PENYONGSANG ARUS TERUS KEPADA ARUS ULANG ALIK

### ABSTRAK

Tesis ini menerangkan secara terperinci reka bentuk dan pembangunan penyongsang satu fasa menggunakan teknik permodulatan lebar denyut sinus. Rekabentuk projek ini terdiri daripada 4 bahagian iaitu litar pengawal, litar pemacu, litar kuasa dan penapis LC. Litar pengawal terdiri daripada pengayun gelombang segi tiga dan pengayun gelombang sinus. Gelombang segi tiga telah dijana dengan menggunakan gabungan pemicu Schmitt dan penyepadu dalam litar pengayun gelombang segi tiga untuk menghasilkan 12V puncak ke puncak pada gelombang 2.326kHz. Manakala gelombang sinus yang gabungan anjakan fasa, voltan berikutan dan penimbal telah menggunakan menghasilkan gelombang 54Hz. Untuk memacu permodulatan lebar denyut sinus kepada pensuisan litar kuasa HCPL-3020 telah digunakan. Manakala di dalam litar kuasa pula, empat peranti IGBT telah digunakan sebagai alat pensusisan. Litar telah dibina di dalam PSIM menggunakan nilai sebenar daripada ujian perkakasan. Manakala nilai di dalam litar PSpice adalah berdasarkan nilai simulasi untuk melihat prestasi keseluruhan pada 310V<sub>DC</sub>. Berdasarkan keputusan simulasi telah mengesahkan bahawa operasi bagi litar penyongsang adalah baik. Selain itu juga, prototaip perkakasan penyongsang telah dilaksanakan dan diuji.

o this term is protected by original copyright

### **CHAPTER 1**

### **INTRODUCTION**

### 1.0 Background

Energy is required to perform any task or to do any type of work. Energy exists in many forms such as electrical energy, mechanical energy, chemical energy, solar energy, thermal energy and etc. As it is well known energy cannot be created or destroyed but can be converted from one form to another. The capability of mankind to generate electricity through transformation of energy is one of the symbols of human civilization. With the cleverness of mankind, electricity is generated and it brings out the mankind from the blackness of night into a bright world (Atanda, 2008). There are two types of electrical power which are DC power and AC power. DC power has constant level of voltage while AC Power has a varying voltage level that oscillates between two voltage levels with specific oscillating frequency. Nowadays, lots of household electrical equipments are running on AC rather than DC. Inverter is a device that is used to convert DC to AC (Rashid, 2004).

Energy can be classified as renewable energy and non-renewable energy. Examples of renewable energies are solar energy, wind energy, biomass energy and hydro energy. Fossil fuels and nuclear fuels are non-renewable energy. Nowadays, renewable energy is getting more and more popular since it produces no harm and no pollution to environment. Photovoltaic (PV) System is another good example for green energy generation. PV system offers a clean, reliable and quiet way for generating electricity. PV system converts sunlight into electricity by solar array (Kate, 2004). The electricity produced is DC. However, most of the electrical appliances require AC power. Inverters are used to convert the DC power from solar panel to AC power that can be used in AC systems. There are several topologies of inverter such as half bridge inverter, full bridge inverter or push pull inverter. Each of the topologies is available in single phase or three phase connection. The single phase full bridge inverter is suitable topology to be used in most of the applications due to the reason that it is suitable to be used with Sinusoidal Pulse Width Modulation (SPWM) switching scheme (Cyril, 1993).

Usually high total harmonics distortion (THD) occurs at the inverter output. Therefore any kind of measurement that can be used to reduce THD at the output becomes an important concern during the development of inverters. For low and medium power applications, square-wave switching may be acceptable. However for high power applications especially in industrial used, the Pulse Width Modulation (PWM) switching technique is more suitable because it can produced a low distorted sinusoidal waveforms. With the availability of high speed power semiconductor devices, the harmonic contents of the output voltage can be minimized or reduced significantly by PWM switching techniques (Xue, 2004). The sinusoidal pulse width modulation (SPWM) switching scheme is the generation of PWM outputs with sinusoidal wave as the modulating signal and triangular wave as the carrier signal. The on and off occurrence of the power switches are determined by comparing sinusoidal wave (modulating) with triangular wave (carrier). The sinusoidal wave determines the frequency of the output waveform while the triangular wave determines the switching frequency of the power transistors (Moorthi, 2005). The combination of SPWM switching technique with LC filter can produce a true sinusoidal wave output that make it compatible with all AC equipments including the sensitive or high rating equipment. There are two main advantages of SPWM which are the amplitude of output voltage can be control by the user and the harmonic content that occur at the output voltage can be decrease just by reducing the value of filter requirements. The output voltage could be fixed or variable at a fixed or variable frequency. A variable output voltage can be srieinal cop obtained by varying the gain of the inverter.

### 1.1 **Problem Statement**

The output voltage waveform for ideal inverters should be sinusoidal. However, in practically it is non-sinusoidal and contains harmonic. The harmonic contents depend to the number of pulses per cycle. Therefore square wave switching method will produce more harmonic contents compared to pulse width modulation switching technique due to number of pulses per cycle for pulse width modulation can be modified by the frequency of triangular carrier waveform (Kjaer, 2005). If higher frequency is used, the numbers of pulses per cycle also increase and at the same time it will reduce the harmonic contents of the inverter. Therefore recently we can see there are increases of research in developing of Sinusoidal pulse width modulation (SPWM) switching scheme. The SPWM techniques are characterized by constant amplitude pulses with different duty cycle for each period (Baharuddin, 2008). The width of this pulses are modulated to obtain inverter output voltage control and to reduce its harmonic content.

In switching losses problem, the number of pulses per cycle also affected. The use of high switching technique will contribute to the high power losses and it also related to the inverter switching design. There are several factors that should be considered in order to meet the requirement such as cost of equipment, size of filter, total harmonic distortion and power loss in switching elements (Baharuddin, 2011). In order to fulfil the requirement, the SPWM switching technique had been analyzed and recommended to be used as a switching device for the single phase full bridge inverter. m original copy

### 1.2 **Objectives**

The objectives of this research work are:

- To select the suitable topology of single phase inverter, study its i. operation and understand its characteristics.

- To test and evaluate the performance of chosen topology by PSIM and ii. PSpice simulation.

To design and implement the hardware of chosen topology and evaluate its performance experimentally.

### **1.3** Thesis Outline

This thesis consists of five chapters and these are organized as follows:

Chapter 1 explains the background of an inverter, the advantages of SPWM method and also problem statement. The overview of project objectives and the overall thesis outline also being discussed in this chapter.

Chapter 2 discusses on literature review of a single phase inverter scheme, driver circuit, switching circuit theory and the calculation which involved in the design. This chapter also reviews the previous work done on single phase inverter.

Chapter 3 describes the methodology adopted to complete this project. The overall design of single phase inverter including the switching strategy and its operation has being explained. The software's used for simulation are also explained.

Chapter 4 explains and discusses all the results that obtained through simulation and hardware testing. The comparison of PSIM simulation results, PSpice simulation results and hardware results are also given in this chapter.

Finally, Chapter 5 discusses the overall conclusion of the single phase full bridge inverter with SPWM switching scheme that is implemented in this project. This chapter also gives the recommendation on future development by just making some additional featured to the circuit.

### **CHAPTER 2**

### LITERATURE REVIEW

### 2.0 Introduction

In this chapter, the types of single-phase inverters and their basic operation is described. The concept and type of Sinusoidal Pulse Width Modulation (SPWM) techniques that are applied to control the output harmonics contents are also described. Furthermore, the work done by other researchers in this area is also discussed briefly in this chapter. The function of each component of inverter circuit is discussed briefly at the end of this chapter.

# 2.1 Single Phase Inverter Topology

For single phase inverter, there are two topologies that are commonly used for conversion of DC power to AC power. These are known as half bridge topology and full bridge topology. Both of the configurations are suitable for low or high power application. The half bridge may sufficient for certain low power applications. However, for high power applications full bridge inverter topology is more suitable. It is most suitable for application that needs output voltage adjustment such as in pulse width modulation techniques (Baharuddin, 2008). Both of these topologies can also be used in high or low voltage DC power supplies.

### 2.1.1 Half Bridge Inverter

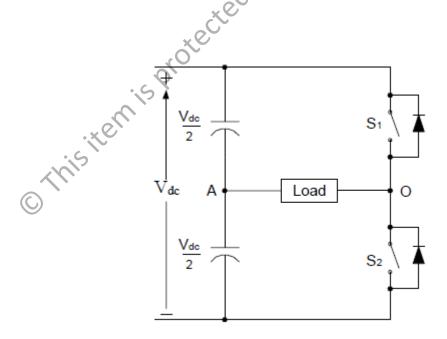

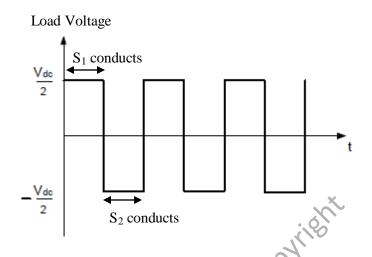

The half bridge is also known as a single leg inverter which is the simplest topology as shown in Figure 2.1. It produces a two-level square wave output waveform using only two semiconductor power switches S1 and S2 as shown in Figure 2.2. For resistive load, the wave shape of load current is identical to the output voltage shape. This topology required a three wire DC source to operate. Both switches, S1 and S2 are never turned on at the same time. If the top switch is closed (on) then the bottom must be open (off) and vice-versa. The basis operation of half bridge inverter can be divided into two operations. If switch S1 is turned on for half of the period the instantaneous output voltage across the load is equal to VDC / 2. If switch S2 is turned on for another half of period then the instantaneous output voltage -VDC / 2 will appear at the load.

Figure 2.1: Half bridge configuration. (Singh, 2011)

Figure 2.2: Two-level output waveform of half bridge configuration.

### 2.1.2 Full Bridge Inverter

Another topology that is known as the full bridge inverter can be used to convert DC power to AC power. It can be used to synthesize a two-level or three-level square-wave output waveform. However, the amplitude of output voltage waveform is double compared to half bridge. There are two inverter legs in a full bridge topology namely as leg a and leg b as shown in Figure 2.3 (Trubitsyn, 2008). A two-level output waveform and three-level output waveform of full bridge single phase inverter are shown in Figure 2.4 and Figure 2.5 respectively. Similarly for full bridge inverter, both leg a and leg b should not be closed (on) at the same time. The operations of single phase full bridge inverter can be divided into two conditions. Practically, when the switches S1 and S2 are turned on the output voltage across the load is equal to +VDC. Then when switches S2 and S3 are on, the output voltage is equal to -VDC. The output voltage will change alternately from positive half period to negative half period. To ensure the switches are not closed (on) at the same time, each gating signal should pass through a protection