# THE OPTIMIZATION OF P-i-N POWER SWITCHING DIODE IN TERM OF REVERSE BREAKDOWN VOLTAGE AND ELECTROSTATIC DISCHARGE PERFORMANCE

By

## SEE JIAN HAO (1431711470)

A thesis submitted in fulfillment of the requirements for the degree of Master of Science in Nanoelectronic Engineering

## INSTITUTE OF NANO ELECTRONIC ENGINEERING UNIVERSITI MALAYSIA PERLIS

2017

## UNIVERSITI MALAYSIA PERLIS

|                                       | DECLARATION OF THESIS |                                                                                                               |  |  |

|---------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Author's full name                    | : SEE JI              | IAN HAO                                                                                                       |  |  |

| Date of birth                         | : 21 Oct              | tober 1988                                                                                                    |  |  |

| Title                                 | : The O <sub>J</sub>  | ptimization of P-i-N Power switching diode in term of reverse                                                 |  |  |

| brea                                  | akdown volt           | tage and ESD performance.                                                                                     |  |  |

| Academic Session                      | : 2016 /              |                                                                                                               |  |  |

| I hereby declare that the             | e thesis beco         | omes the property of Universiti Malaysia Perlis (UniMAP) and to be placed at the library                      |  |  |

| of UniMAP. This thesis                | is classified         | d as:                                                                                                         |  |  |

| CONFIDEN                              | TIAL                  | (Contains confidential information under the Official Secret Act 1972)*                                       |  |  |

| RESTRICT                              | ED                    | (Contains restricted information as specified by the organization where research was done)*                   |  |  |

| OPEN ACCESS                           |                       | I agree that my thesis is to be made immediately available as hard<br>copy or on-line open access (full text) |  |  |

| I, the author, give permi             | ission to the         | e UniMAP to reproduce this thesis in whole or in part for the purpose of                                      |  |  |

| research or academic ex               | change only           | ly (except during a period of 5 years, if so requested above).                                                |  |  |

| OT T                                  | 12                    | Certified by:                                                                                                 |  |  |

| ~~~~,                                 | 7                     |                                                                                                               |  |  |

| SIGNATURE                             |                       | SIGNATURE OF SUPERVISOR                                                                                       |  |  |

| SEE JIAN HAO                          |                       | Ir. Dr. Mohd Khairuddin Md Arshad                                                                             |  |  |

| 881021-07-5259<br>(NEW IC NO. / PASSI | PORT NO.              | .) NAME OF SUPERVISOR                                                                                         |  |  |

| Date :                                |                       | Date :                                                                                                        |  |  |

|                                       |                       |                                                                                                               |  |  |

#### ACKNOWLEDGEMENT

The way to achieve this journey has never been easy. This three years journey is a road of responsibility, excitement, and experience that full with uncertain matters that reshaped my life to become a stronger, better and matured person. It never been an easy task and it never was, but the support from people around me, lift me up, allow me to strive for this triumph. There are no excuses for me not to acknowledge the person that voluntarily walk this winding road together, as an appreciation and memories.

I would like to thank Universiti Malaysia Perlis (UniMAP), School of Microelectronic Engineering (SoME) and specifically Institute of Nano electronic Engineering (INEE) for providing me with exceptional three years of trials and tribulations. Most of all, the excellent facilities are truly appreciated.

For my supervisor, Assoc. Prof. Ir. Dr. Mohd Khairuddin bin Md. Arshad, I would like to express my sincere gratitude to him for the continuous support of my master degree study and related research. I appreciate a lot for his patience, motivation, and great knowledge. I have learned a lot from him, his expertise in fabrication and device theory have made me gain a lot of knowledge in device knowledge. His guidance helped me along research and writing of this thesis. His way of refining me surely is remain beneficial for myself and people around me.

Last but not the least; I would like to thank my beloved family. I feel thankful on the unconditional love and sacrifice that my mother Wong Bee Choo, and my father See Boon Aun have given to me. Besides, I would like to thank my god brother, Wong Shiak Sun who constantly giving me the encouragement and support in my research studies throughout writing this thesis for three years. Eventually, now I am climbing up towards success, just to bring cheerful moment for them. I hope I can see one of the greatest smile from them both, and the reason behind that smile is me.

othis tem

### TABLE OF CONTENTS

| DECLA          | RATION OF THESIS                                                                                                                                                               | PAGE<br>i |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| ACKNO          | DWLEDGEMENT                                                                                                                                                                    | ii        |

| TABLE          | <b>OF CONTENTS</b>                                                                                                                                                             | iii       |

| LIST O         | F FIGURES                                                                                                                                                                      | vi        |

| LIST O         | FTABLES                                                                                                                                                                        | ix        |

|                |                                                                                                                                                                                |           |

| LISTO          | FABBREVIATIONS                                                                                                                                                                 | X         |

| LIST O         | F SYMBOLS                                                                                                                                                                      | xii       |

| ABSTR          | AK                                                                                                                                                                             | xiii      |

| ABSTR          | ACT                                                                                                                                                                            | xiv       |

| СНАРТ          | F TABLES<br>F ABBREVIATIONS<br>F SYMBOLS<br>AK<br>ACT<br>ER 1: INTRODUCTION<br>Background<br>Problem statements<br>Research objective<br>Research scope<br>Thesis Organization |           |

| 1.1            | Background                                                                                                                                                                     | 1         |

| 1.2            | Problem statements                                                                                                                                                             | 4         |

| 1.3            | Research objective                                                                                                                                                             | 7         |

| 1.4            | Research scope                                                                                                                                                                 | 9         |

|                |                                                                                                                                                                                | 10        |

|                | ER 2: LITERATURE REVIEW                                                                                                                                                        |           |

| C              | Introduction                                                                                                                                                                   | 12        |

| 2.2            | P-N diode                                                                                                                                                                      | 12        |

| 2.2.1<br>2.2.2 |                                                                                                                                                                                | 14        |

| 2.2.2          |                                                                                                                                                                                | 15<br>16  |

| 2.2.5          | P-i-N diode                                                                                                                                                                    | 10        |

| 2.5            |                                                                                                                                                                                |           |

| design         |                                                                                                                                                                                | 20        |

| 2.4            | ESD performance                                                                                                                                                                | 23        |

| 2.5            | Electric field                                                                                                                                                                 | 23        |

| 2.6            | P-i-N diode applications                                                                                                                                                       | 31        |

| 2.7   | Design of experiment                                                                                                                                                                             | 32 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.8   | Chapter summary                                                                                                                                                                                  | 33 |

| СНАРТ | ER 3: RESEARCH METHODOLOGY                                                                                                                                                                       |    |

| 3.1   | Introduction                                                                                                                                                                                     | 34 |

| 3.2   | Overview of the fabrication processes and characterization study                                                                                                                                 | 34 |

| 3.3   | TCAD simulation                                                                                                                                                                                  | 37 |

| 3.3.1 | Structure editor                                                                                                                                                                                 | 38 |

| 3.3.2 | Process simulation                                                                                                                                                                               | 39 |

| 3.3.3 |                                                                                                                                                                                                  | 39 |

| 3.4   | Design of experiment and evaluation criteria                                                                                                                                                     | 40 |

| 3.4.1 | Design of experiment and evaluation criteria<br>Epitaxial layer evaluation approach<br>1.1 TCAD simulation of epitaxial layer evaluation<br>1.2 DOE of epitaxial layer wafer fabrication process | 40 |

| 3.4   | 1.1 TCAD simulation of epitaxial layer evaluation                                                                                                                                                | 41 |

| 3.4   | 1.2 DOE of epitaxial layer wafer fabrication process                                                                                                                                             | 43 |

| 3.4   | 1.3 Electrical characterization on DOE of epitaxial layer wafer                                                                                                                                  | 45 |

| 3.4.2 |                                                                                                                                                                                                  |    |

|       | junction                                                                                                                                                                                         | 46 |

|       | 2.1 TCAD simulation of P+ anode junction evaluation                                                                                                                                              | 46 |

|       | 2.2 DOE of P+ anode junction wafer fabrication process                                                                                                                                           | 47 |

| 3.4   | 2.3 Electrical characterization on DOE of P+ anode junction wafer                                                                                                                                | 50 |

| 3.5   | Wafer fabrication flow for P-i-N power switching diode                                                                                                                                           | 50 |

| 3.5.1 | Starting material (water substrate bulk with epitaxial layer)                                                                                                                                    | 51 |

| 3.5.2 | 2 Initial oxide                                                                                                                                                                                  | 52 |

| 3.5.3 | 5 Photolithography                                                                                                                                                                               | 54 |

| 3.5.4 | Etch                                                                                                                                                                                             | 55 |

| 3.5.5 | Boron coaring and Diffusion process                                                                                                                                                              | 56 |

| 3.5.6 | TEOS layer deposition process                                                                                                                                                                    | 57 |

| 3.5.7 | Annealing treatment                                                                                                                                                                              | 58 |

| 3.5.8 | 8 N+ isolation formation                                                                                                                                                                         | 59 |

| 3.5.9 | 4 k Low Thermal oxide with anneal                                                                                                                                                                | 59 |

| 3.5.1 | 0 Platinum target and platinum diffusion                                                                                                                                                         | 60 |

| 3.5.1 | 1 Metallization process (metal contact)                                                                                                                                                          | 61 |

| 3.5.1 | 2 Nitride passivation deposition process                                                                                                                                                         | 62 |

| 3.5.1 | 3 Wafer thinning, back metal deposition and sinter                                                                                                                                               | 63 |

| 3.6   | Device characterization test                                                                                                                                                                     | 64 |

| 3.6.1 | Electrical test                                                                                                                                                                                  | 64 |

| 3.6.2 | E ESD test                                                                                                                                                                                       | 66 |

| 3.6.2.1 ESD human body model test                                                                                                                                                                                                                                                                                                                  | 66  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.6.2.2 ESD machine model test                                                                                                                                                                                                                                                                                                                     | 68  |

| 3.7 Chapter summary                                                                                                                                                                                                                                                                                                                                | 69  |

| CHAPTER 4: RESULT AND DISCUSSION                                                                                                                                                                                                                                                                                                                   |     |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                   | 70  |

| 4.2 Characterization of power switching diode                                                                                                                                                                                                                                                                                                      | 70  |

| 4.2.1 The effects of epitaxial layer in P-i-N switching diode for high power devices.                                                                                                                                                                                                                                                              | 71  |

| 4.2.1.1 Simulation result                                                                                                                                                                                                                                                                                                                          | 71  |

| 4.2.1.2 DOE wafer result                                                                                                                                                                                                                                                                                                                           | 74  |

| 4.2.2 ESD improvement of switching diode through introducing a lighter and deeper                                                                                                                                                                                                                                                                  |     |

| anode junction                                                                                                                                                                                                                                                                                                                                     | 79  |

| 4.2.2.1 Simulation result                                                                                                                                                                                                                                                                                                                          | 79  |

| 4.2.2.2 Design of experiment result                                                                                                                                                                                                                                                                                                                | 83  |

| 4.3 Chapter summary                                                                                                                                                                                                                                                                                                                                | 89  |

| CHAPTER 5: CONCLUSION                                                                                                                                                                                                                                                                                                                              |     |

| 5.1 Conclusions                                                                                                                                                                                                                                                                                                                                    | 90  |

| 5.2 Suggestions for future work                                                                                                                                                                                                                                                                                                                    | 91  |

| REFERENCES                                                                                                                                                                                                                                                                                                                                         | i   |

| APPENDICES                                                                                                                                                                                                                                                                                                                                         | v   |

| LIST OF PUBLICATIONS                                                                                                                                                                                                                                                                                                                               | xii |

| SKO                                                                                                                                                                                                                                                                                                                                                |     |

| ·SX                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                    |     |

|                                                                                                                                                                                                                                                                                                                                                    |     |

|                                                                                                                                                                                                                                                                                                                                                    |     |

| <ul> <li>4.2.2 ESD improvement of switching diode through introducing a lighter and deeper anode junction</li> <li>4.2.2.1 Simulation result</li> <li>4.2.2.2 Design of experiment result</li> <li>4.3 Chapter summary</li> </ul> CHAPTER 5: CONCLUSION 5.1 Conclusions 5.2 Suggestions for future work REFERENCES APPENDICES LIST OF PUBLICATIONS |     |

|                                                                                                                                                                                                                                                                                                                                                    |     |

### LIST OF FIGURES

| NO.            |                                                                                                                                                                                         | PAGE     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1            | 2D structure layer P-i-N diode                                                                                                                                                          | 3        |

| 1.2            | Cross-Section structure of Power Switching Diode                                                                                                                                        | 4        |

| 1.3(a)         | Top view of SEM images of ESD failures diode after de-processing<br>and decorative etches. The metal spike dots that indicated as the red<br>arrow are confined at the edge of junction | 7        |

| (b)            |                                                                                                                                                                                         | 7        |

| 2.1            | Cross section illustration of the diode region<br>P-N junction diode schematic structure                                                                                                | 13       |

| 2.2            | P-N Depletion region diagram in equilibrium state                                                                                                                                       | 13       |

| 2.3            | P-N junction during forward bias state                                                                                                                                                  | 15       |

| 2.4            | P-N junction during equilibrium state and reverse bias state                                                                                                                            | 16       |

| 2.5            | IV characteristics of an ideal power diode                                                                                                                                              | 17       |

| 2.6            | IV electrical characteristics of a non-ideal diode                                                                                                                                      | 18       |

| 2.7            | P-i-N junction diode schematic structure                                                                                                                                                | 19       |

| 2.8(a)         | Comparison of ideal (a) P-N junction in terms of (i) 2D structure and (ii) electrical field distribution                                                                                | 21       |

| (b)            | Comparison of ideal (b) P-i-N diode in terms of (i) 2D structure and (ii) electrical field distribution                                                                                 | 21       |

| 2.9            | 3D of anode junction curvature                                                                                                                                                          | 24       |

| 2.10(a)<br>(b) | Junction breakdown mechanism for shallower junction planar diode<br>Junction breakdown mechanism for deeper junction planar diodes                                                      | 27<br>27 |

| 3.1            | The overall process flow power switching diode optimization                                                                                                                             | 36       |

| 3.2            | The framework of TCAD simulation                                                                                                                                                        | 38       |

| 3.3            | Diode Device structure with doping profile distribution                                                                                                                                 | 43       |

| 3.4            | Wafer starting material from supplier with epitaxial layer deposited                                                                                                                    | 44       |

| 3.5(a)         | Two level factorial of DOE, Factor A and B refer to epitaxial layer thickness and epitaxial layer resistivity respectively                                                              | 45       |

| (b)            | The location of four corners and centre of the evaluation samples                                                                                                                       | 45       |

consists of group A, B, C, D and E

| 3.6  | P+ anode junction edges curvature profile for a) shallower junction depth planar diode, b) deeper junction depth planar diodes | 49 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | P-i-N power switching diode fabrication process flow                                                                           | 51 |

| 3.8  | The raw substrate that consists of bulk substrate and epitaxial layer                                                          | 52 |

| 3.9  | The wafer substrate with an 8 kA oxide layer grown on top of epitaxial layer                                                   | 54 |

| 3.10 | P+ anode junction opening using oxide                                                                                          | 56 |

| 3.11 | Spin boron coating on top of wafer surface                                                                                     | 56 |

| 3.12 | P+ anode junction formation in the N- epitaxial layer                                                                          | 57 |

| 3.13 | 2.6 kA TEOS deposited on top of processed wafer                                                                                | 58 |

| 3.14 | Oxide anneal process that increase the depth of the P+ anode junction                                                          | 58 |

| 3.15 | N+ isolation region formation                                                                                                  | 59 |

| 3.16 | Low Thermal oxide deposited on top of the wafer                                                                                | 60 |

| 3.17 | Platinum target is sputtered at the back of the wafer                                                                          | 60 |

| 3.18 | Thin film of AlSi metal layer is deposited on top of the wafer surface                                                         | 62 |

| 3.19 | Thin film of Nitride passivation layer is deposited on top of the wafer surface                                                | 62 |

| 3.20 | Final cross section of power switching diode with wafer thinning<br>and Gold reverse wafer deposited                           | 63 |

| 3.21 | The Electroglas model wafer probe tester                                                                                       | 65 |

| 3.22 | Tektronix 370 model Curve tracer                                                                                               | 65 |

| 3.23 | Illustration of Human body model ESD test                                                                                      | 67 |

| 3.24 | An oscilloscope measurement during of Human body model ESD                                                                     | 67 |

| 3.25 | Illustration of Machine model ESD test                                                                                         | 68 |

| 3.26 | An oscilloscope measurement during of Machine model ESD                                                                        | 69 |

| 4.1(a | a) Current- voltage characteristics under reverse bias for different epitaxial thicknesses and dopant concentrations                                                       | 71 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| (1    | <ul> <li>b) Current- voltage characteristics under forward bias for different<br/>epitaxial thicknesses and dopant concentrations</li> </ul>                               | 71 |

| 4.2   | Statistical data on the impact of epitaxial thickness and resistivity of the fabricated devices                                                                            | 76 |

| 4.3(  | · •                                                                                                                                                                        | 78 |

| (     | b) $V_{BR}$ at 100 µA qualification lot electrical distribution                                                                                                            | 78 |

| 4.4(a | a) Total current density doping profile distribution of an un-zoom junction profile                                                                                        | 80 |

| ()    | b) Total current density doping profile distribution of Control group:<br>zoomed junction profile with 1 x $10^{16}$ atom/cm <sup>2</sup> and junction depth<br>of 1.69 µm | 80 |

| ((    | c) Total current density doping profile distribution of Group a:<br>zoomed junction profile with $1 \ge 10^{16}$ atom/cm <sup>2</sup> and junction depth<br>of 4.69 µm     | 80 |

| (0    | d) Total current density doping profile distribution of Group b:<br>zoomed junction profile with 5 x $10^{15}$ atom/cm <sup>2</sup> and junction depth<br>of 4.69 µm       | 80 |

| 4.5(a | a) Impact ionization doping profile distribution of un-zoom junction profile                                                                                               | 82 |

| (1    | b) Impact ionization doping profile distribution of Control group:<br>junction profile with $1 \times 10^{16}$ atom/cm <sup>2</sup> and junction 1.69 µm depth             | 82 |

| (0    | c) Impact ionization doping profile distribution of Group a: junction profile with 1 x $10^{16}$ atom/cm <sup>2</sup> and 4.69 µm junction depth                           | 82 |

| (0    | d) Impact ionization doping profile distribution of Group b: junction profile with 5 $\times 10^{15}$ atom/cm <sup>2</sup> and 4.69 µm junction depth                      | 82 |

| 4.6   | V <sub>F</sub> wafer probe data at 200mA                                                                                                                                   | 84 |

| 4.7   | $V_{BR}$ wafer probe data at 5 $\mu A$                                                                                                                                     | 85 |

| 4.8   | $\bigcirc$ I <sub>R</sub> wafer probe data @ 260V                                                                                                                          | 86 |

### LIST OF TABLES

| NO. |                                                                                                                                            | PAGE |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1 | Simulation thickness and concentration dosage of N- layer                                                                                  | 42   |

| 3.2 | Substrate 4 corner split table                                                                                                             | 44   |

| 3.3 | Simulation of junction depth and the implant dose concentration of P+ anode Junction                                                       | 46   |

| 3.4 | DOE split on the Boron pre-deposition process and junction diffusion process                                                               | 48   |

| 4.1 | ESD result on evaluation lot in HBM and MM compared to control group                                                                       | 86   |

| 4.2 | Summary table of DOE evaluation group compared to control group on mean value of electrical wafer test data and ESD surge test performance | 88   |

| 4.3 | Final fixed Process changes for Group C                                                                                                    | 88   |

| 4.4 | Summary table for ESD HBM & MM data                                                                                                        | 88   |

|     |                                                                                                                                            |      |

#### LIST OF ABBREVIATIONS

- $I_R$ Reverse Leakage Current

- $V_{BR}$ Reverse Breakdown Voltage

- $V_{\rm F}$ Forward Voltage

- ESD Electrostatic Discharge

- HBM Human Body Mode

- MM Machine Mode

- CDM Charge Device Mode

- .gn of othat copyright Technology Computer-aided Design TCAD

- DOE Design of Experiment

- Reverse Recovery Lifetime TRR

- Response Surface Mode RSM

- TEOS Tetraethylorthosilicate

- CVD Chemical Vapor Deposition

- Plasma Enhanced Chemical Vapor Deposition PECVD

- **PVD** Physical Vapor Deposition

- LTO(G) Low Thermal Oxide

- CMP **Chemical Mechanical Planarization**

- DUT **Device Under Test**

- IC **Integrated Circuit**

- SEM Scanning Electron Microscope

- GUI Graphical User Interface

- Sentaurus Work Bench SWB

- 1D One dimensions

- 2D Two dimensions

- 3D Three dimensions

- Hexamethyldisilazane HMDS

- OVAT One Variable at a Time

- Buffered oxide wet etching BOE

othis tern is protected by original copyright

#### LIST OF SYMBOLS

- $I_R$ Reverse Leakage Current

- Reverse Breakdown Voltage  $V_{BR}$

- V<sub>F</sub> Forward Voltage

- Forward Current  $I_F$

- Р Positive Dopant

- Ν Negative Dopant

- , protected by original copyright ESD Electrostatic Discharge

- °C Celsius

- Ångström Å

- Si Silicon

- Oxygen Gas  $O_2$

- SiO<sub>2</sub> Silicon Oxide

- $H_2O$ Water

- Hydrogen Gas  $H_2$

- Silicon Aloy AlSi

- Dopant Concentration N<sub>D</sub>  $(\mathbf{C})$

- Depletion Width  $W_D$

- Micron μ

- Mili m

#### Pengoptimasi P-i-N Kuasa Pensuisan dalam Voltan Pincang Balikan dan Prestasi Nyahcas Elektrostatik

#### ABSTRAK

Kuasa pensuisan penerus (P-i-N penerus) merupakan salah satu penerus yang digunakan secara meluas dalam tinggi peranti semikonduktor kuasa sebagai perlindungan litar. Populariti ini terhasil daripada kecemerlangan untuk menyekat voltan terbalik dan prestasi nyahcas elektrostatik yang tinggi. Oleh itu, penerokaan penerus kuasa untuk membuat peranti yang lebih mantap dan berdaya saing dalam pasaran adalah tidak terbatas, yang bertujuan untuk penambahbaikan yang berterusan ke atas ciri-ciri elektrik. Dalam tesis ini, struktur rekabentuk kuasa pensuisan penerus P-i-N telah digunakan terdiri daripada bentuk anod persimpangan yang berbentuk lingkaran, substrat jenis N dengan lapisan epitaksi substrat silikon yang mewakili kawasan intrinsik. Terdapat dua jenis kuasa pensuisan penerus P-i-N dibincangkan dalam tesis ini, iaitu 250 V dan 300 V semasa pincang balikan. Kajian peningkatan prestasi voltan puncang balikan dan prestasi pembaikan nyahcas elektrostatik (ESD) yang berbeza telah dilancarkan masing masing. Perubahan tersebut telah dilakukan melalui proses simulasi serta rekabentuk disahkan melalui eksperimen proses wafer fabrikasi secara DOE. Untuk analisa ESD, peranti telah melalui pengujian tanpa musnah (non-destructive test) dan pengujian musnah (destructive test) untuk peranti yang telah difabrikasi. Pada mulanva, tesis membincangkan kajian kajian penyelidikan untuk memperluaskan julat operasi kuasa pensuisan daripada 250 V kepada lebih daripada 300 V semasa pincang balikan berdasarkan perubahan ketebalan dan kerintangan lapisan epitaxi semasa pincangan arus hadapan dan balikan. Tujuan memperluaskan julat operasi kuasa pensuisan adalah digunakan dalam aplikasi kuasa pengagihan kuasa dan bukan dalam aplikasi telekomunikasi sahaja. Hasil kajian menunjukkan bahawa, perubahan tersebut dapat meningkatkan prestasi voltan kepada tahap ~500 V, iaitu melebihi 300 V semasa arus balikan. Peningkatan prestasi voltan pincang balikan adalah lebih daripada 65% dari 250 V. Selain daripada kajian meningkat ciri-ciri elektrik dalam tesis, kajian pembaikan ESD penerus P-i-N juga telah ditunjukkan dengan diod 300 V semasa arus balikan. Penambahbaikan ESD penerus P-i-N boleh dicapai dengan mengubah profil ciri-ciri persimpangan anod P+ dalam penerus P-i-N. Ciri-ciri profil juga boleh diubah dengan merendahkan kepekatan pendopan dan meningkatkan kedalaman persimpangan anod penerus P-i-N. Ianya didapati, untuk 300 K penerus P-i-N dapat bertahan lonjatan voltan lebih daripada 1 kV semasa ESD ragam badan manusia (HBM) ( 400% tinggi daripada asal) dan lebih daripada 400 V semasa ESD ragam mesin (MM) (100% tinggi daripada asal).

#### The Optimization of P-i-N Power Switching Diode in Term of Reverse Breakdown Voltage and Electrostatic Discharge Performance

#### ABSTRACT

The Power switching diode (P-i-N diode) is one of the widely used diode in high power semiconductor devices as circuit protection. This popularity comes from excellent reverse voltage blocking and better electrostatic discharge (ESD) performance. As a result, the exploration on the P-i-N power switching diode to make the device more robust and competitive in the market is boundless, which aims for continuous improvement on the electrical characteristics. In this thesis, the design structure of P-i-N power switching diode consist of a circular shape anode junction, an n-type bulk substrate and the epitaxial layer of silicon substrate that represent the intrinsic region is used. Two different type of reverse breakdown voltage range P-i-N power switching diode are discussed in this thesis which is 250 V and 300 V. Independently, the optimization of reverse breakdown voltage and ESD respectively is conducted using 250 V and 300 V respectively as both diode have different good and poor electrical performance. The improvement of both diodes are performed by process simulation and as well as the confirmation by the design of experiment (DOE) of physical wafers fabrication process. For the ESD analysis, the devices are then subjected to nondestructive and destructive test of the fabricated diodes. Initially, this thesis describes the research work to widen the operating range of the 250 V P-i-N power switching avalanche diodes that can be operated more than 300 V by exploring the effects of the thickness and resistivity of epitaxial layer during forward and reverse biasing. Purpose of widen the operating range is to be used in power distribution application instead of telecommunication application. The result shows that, the changes on a P-i-N type structure of the power switching avalanche diode can increase the reverse breakdown voltage performance to ~500 V, which is beyond 300 V during reverse bias. The improvement of reverse breakdown voltage is more than 65% from 250 V. In addition to the electrical characteristics operating range improvement in the thesis, the study of ESD improvement of 300 V reverse breakdown voltage P-i-N diode is demonstrated. A better ESD performance of the P-i-N diode is also achieved by changing the characteristic profile of the P+ anode junction of P-i-N diode. The characteristics profiles are altered by lightening the dopant concentration and increasing the depth of the P-i-N diode junction. It is found that, the 300V P-i-N power switching diode can sustain more than 1 kV during ESD Human Body Modal (HBM) surge test (400% higher from initial surge) and more than 400 V during ESD Machine Modal (MM) surge test (100% higher from initial surge).

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 Background**

A semiconductor material has a small energy gap (i.e., 1.11 eV for silicon), that is a value between an insulator (>2 eV) and a conductor (0 eV) (M. Quirk & J. Serda , 2001). Thus, a semiconductor material can function as either conductor or insulator. For a formation of diode, a P-N junction is created with p-type and n-type semiconductor materials in intimate contact on an atomic scale. The formation of P-N junction is to diffuse acceptor impurities (p-type dopant) into an n-type silicon crystal or vice versa. The depletion region formed instantaneously across a P-N junction when junction is in thermal equilibrium or in a steady state. During the steady state, the properties of the system does not vary in time; thus it has been called dynamic equilibrium (J. E. Ayers , 2003) (S.M. Kang and Y. Leblebici, 2003).

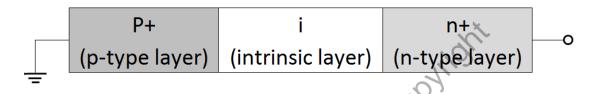

A P-N junction diode is a device which only allows unidirectional of current flow when operating within a rated specified voltage level, and it is also known as a rectifier. In high power applications, an ideal power diode should be able of conducting high forward bias current ( $I_F$ ) and supporting high reverse breakdown voltage ( $V_{BR}$ ) (B. J. Baliga, 1996). For a vertical structure of P-N junction diode, a very thick wafer substrate bulk can be used to fulfill the requirement of a power diode. However, thicker substrate exhibits several drawbacks, which are greater weight and higher production cost. One of the methods for having a higher reverse breakdown voltage and higher forward current performance is by using the P-i-N diode's structure. The P-i-N diode was one of the very first semiconductor devices developed for the power circuit application. (B. J. Baliga ,1996) This evolution came from a conventional P-N junction diode with the addition of an extra intrinsic layer deposited between p-type and n-type regions. Figure 1.1 illustrates the P-i-N diode structure in 2D structure.

Figure 1.1: 2D structure layer P-i-N diode

The P-i-N diode has an intrinsic layer known as the i-region, which can be depleted at zero bias. Hence, an ideal P-i-N diode is also called a zero punch through diode (J. F. White , 2012) However, in practical cases, not all diodes are zero punch through. The i-region (sandwiched between the heavily doped p and n regions) is being substituted by a substantially higher resistivity p- or n-type layer (J. F. White , 2012).

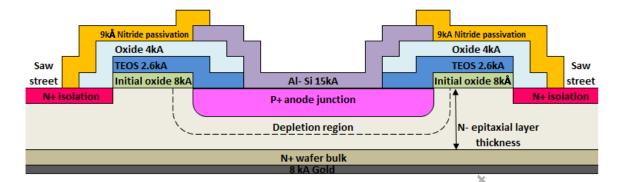

In semiconductor power device theory, the reverse breakdown voltage of P-i-N is controlled by the intrinsic layer which represented by the n- epitaxial layer of the diode structure. Figure 1.2 illustrates the cross section design of the power switching diode.

Figure 1.2: Cross-Section structure of Power Switching Diode

Compared to a normal P-N junction diode, the structure of P-i-N diode supports a higher reverse breakdown voltage with a much thinner n-type substrate. The heavily doped boron, p+ region is closest to the top of the diode. The doping level changes abruptly at the heavily doped boron p+ junction to a flat n- region; again abruptly to the flat n+ doping in the diode's another side (A. A.Sweet , 2007)

With the better reverse breakdown voltage performance ( $V_{BR}$ ) of P-i-N diode compared with P-N junction diode, the usage of the P-i-N diode is still limited in power switching performance. P-i-N power switching diode is widely used in power industry. There are three main performance criteria that need to be achieved for the power switching diode which are huge reverse breakdown voltage, switching performance and the ESD performance. The ESD performance must be substantially high in power switching industry as ESD can create spectacular electric sparks under a huge surge which can cause damage to sensitive electronic devices. To improve reverse breakdown voltage and ESD performance, the design of the device must be studied and modified.

This research is greatly motivated by the comprehension of the function of power switching diode with vertical P-i-N diode structure. Two commercially available P-i-N power switching diode devices, 250 V and 300 V are the interest in this work. The design of both 250 V and 300 V are similar except the die size. 250 V power switching diode has die size of 468  $\mu$ m x 468  $\mu$ m while 300 V power switching diode has a smaller die size of 400  $\mu$ m x 400  $\mu$ m.

#### **1.2 Problem statements**

In this work, two main performance criteria will be focused on which are the studies of increase reverse breakdown voltage and the ESD performance improvement. The device failure for these two types of diode encourages us to explore and to understand the problem. The failures are low breakdown voltage for 250 V power switching diode and poor ESD performance for 300 V power switching diode. The device optimization of both 250 V and 300 V P-i-N power switching diode are done independently, as both limitation are different.

Limitation of the operating range less than 300 V is found on the 250 V P-i-N power switching diode which unable to use in the motor control, robotics and power distribution application. In this thesis, we propose to increase the reverse breakdown voltage from 250 V to 450 V. The reason of increasing reverse breakdown voltage of 250 V power switching diode is to widen the application operating range from only used in the application of computer and telecommunications.

To increase the reverse breakdown voltage, this work will discuss the power switching diode reverse breakdown improvement through N- epitaxial layer optimization approach.

The alteration of the N- epitaxial layer thickness and resistivity profile not only increase the reverse breakdown voltage but may unpredictable significant increase other electrical performance such as forward voltage,  $V_F$  and reverse leakage current,  $I_R$ . So, for this 250 V power switching diode research approach, the key analysis and investigation of exploring a good working window is assisted by Technology computer-aided design (TCAD) simulation and wafer fabrication Design of Experiment (DOE) method.

As for 300 V power switching diode, the focus is on the ESD improvement. This power switching diode has the same cross section structure design as the 250 V which is shown in Figure 1.2, except the smaller die size of 400 µm x 400 µm. Typically, as the feature chip size is smaller and complexity of semiconductor fabrication technology is more, resolving ESD-induced reliability issues have become more challenging.(Z. Qiang Cui, Juin J. Liou, Jean-Jacques Hajjar, Javier Salcedo, 2015). Therefore, by comparing the ESD performance of 250 V and 300 V power switching diode units, the 250 V P-i-N power switching diode can sustain more than 1 kV surge during ESD HBM and more than 400 V surge during ESD MM due to the larger die size. But for 350 V P-i-N power switching diode with a smaller die size, it can only sustain less than 500 V surge during ESD HBM and less than 400 V surge during ESD MM.

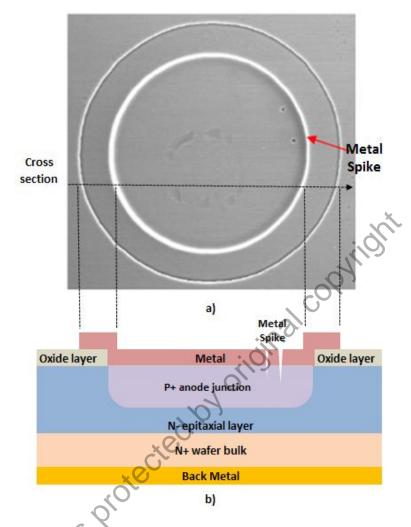

In this work, failure analysis on poor ESD performance units from 300 V P-i-N power switching diode is performed too observe the detail magnification image of the failure spot. After de-processing and decorative etch on the sample, the metal spike damage observed under the Scanning Electron Microscope (SEM) in the diode is confined to edges of the junction as shown in Figure 1.3.

Figure 1.3: a) Top view of SEM images of ESD failures diode after de-processing and decorative etches. The metal spike dots that indicated as the red arrow are confined at the edge of junction b) Cross section illustration of the diode region

In Figure 1.3, the arrows indicate the weak points for the planar diode at the anode junction curvature where the exhibits the highest junction parasitic capacitance. During the ESD surge testing, the high current cause local heating in short timescale where the design of the junction does not allow heat flow to the surrounding regions equally. A hot spot can form and lead to metal migration and short-circuit of the junction. This metal migration is called metal spike. The red arrows indicate the metal spike which is the weak points for the planar diode at the anode junction curvature in Figure 1.3. These failures are further shown

to be caused by poor ESD. In order to study the improvement of the ESD performance, 300 V power switching diode available commercial device is used. The exploration and study of the P+ anode junction curvature profile changes in term of altering the resistivity and the junction depth of the P+ anode junction is carried out.

The diffusion of the P+ dopant into N- epitaxial layer will cause the junction depth of the N- region to be shortened. The deeper the junction depth of the P+ region, the shallower will be junction depth of the N- region. Thus lower reverse breakdown voltage will be obtained which due to more of the intrinsic region is consumed to form a P+ region. So, to improve the ESD performance of the power switching diode through the changes of the P+ anode junction depth and resistivity, a reduction of the reverse breakdown voltage will need to take into consideration. A series of the TCAD simulation and DOE will be performed to shows the effects of the anode junction formation process time and temperature on the ESD performance of the 300 V switching diode.

Whereas for the switching performance will not take into account of the both 250 V and 300 V P-i-N power switching diode optimization. The is because the key process of platinum diffusion to determine the switching performance is done after the N- epitaxial layer and P+ anode junction profile optimization.

#### **1.3 Research objective**

The objectives of the research can be summarized as follows.

To improve 250 V power switching diode (with die size of 468 μm x 468 μm) reverse bias breakdown voltage through epitaxial layer optimization using TCAD simulation and DOE. To improve ESD performance of 300 V power switching diode (with die size of 400  $\mu$ m x 400  $\mu$ m) through the P+ anode junction profile characteristic in term of junction depth and resistivity using TCAD simulation and DOE.

Two commercially available power switching diode devices are the interest in this work which are 250 V and 300 V. The device failure for these two types of diode encourages us to explore and to understand the problem. The failures are low breakdown voltage for 250 V power switching diode and poor ESD performance for 300 V power switching diode.

For the first objective, 250 V P-i-N power switching diode with larger die size of 468  $\mu$ m x 468  $\mu$ m are used to investigate the effects of changes in intrinsic i-region width on the reverse bias current-voltage (I-V) performances. The intrinsic i-region is referring to the N-epitaxial layer of the substrate. In this thesis, the objective is to increase the reverse breakdown voltage from 250 V to 450 V. The reason of increasing reverse breakdown voltage is to widen the operating range of the switching avalanche diode that can be operated more than 300 V. Since P-i-N diode operates in a thickness-limited mode, which is controlled by the width of n- epitaxial layer i-region, the factors need to be taken into consideration is the epitaxial layer specification which includes epitaxial thickness and epitaxial resistivity. The given specification for epitaxial thickness is from 34 – 42  $\mu$ m with resistivity ranges from 26 – 32 ohm.cm. With the fixed P+ anode junction depth, we will monitor the variable of the epitaxial thickness and resistivity that give us the reverse breakdown voltage of 450 V.

For the second objective, the attention will focus on the ESD performance improvement of the 300 V power switching diode with die size of 400  $\mu$ m x 400  $\mu$ m. The power switching diode of 300 V has a smaller die size compare to 250 V power switching

diode. With the same diode cross section design, the P-i-N power switching diode structure consists of circular shaped boron diffused P+ anode junction into the intrinsic region. The profile of the P+ anode junction can be changed by changing the process drive time and process temperature of the boron pre-deposition process and diffusion process.

#### **1.4 Research scope**

The research scope in this research is mainly divided into four main stages. The initial stage of this research includes identifying the existing problem of both low range (< 300 V) and high range (> 300 V) voltage power switching diode.

Second stage of the research scope is about validating for the improvement hypothesis of power switching diode via TCAD simulation.

For third stage of research scope, the implementation of the improvement that validated from the TCAD simulation result on the wafer fabrication using DOE approach. During the third stage, validation with fabrication of power switching diode is executed to get the real result. The DOE method is applied in the third part together with power switching diode fabrication to prepare samples for analysis and verification. Fabrication of a power switching diode included oxidation, photolithography, etching and metallization process.

Once fabrication processes completed, the samples are tested for its functionality as the fourth stage. Functionality test can be divided into two types which are the nondestructive test and destructive test. The non-destructive functionality test included electrical testing to check for the forward voltage, reverse leakage current and reverse breakdown voltage. The destructive analysis in this work scope includes the ESD surge test on human body model (HBM) and machine model (MM). The non-destructive device characterization analysis is performed using JMP statistical software on the electrical characteristic. The core of the electrical testing is to validate the hypothesis in earlier stage. Multiple units across variety of process groups wafers will be tested using probe tester. The multiple data point will be compiled using JMP statistical software to monitor the electrical performance data distribution. With the final confirmation analysis result that obtained with JMP statistical software, a verification process to repeat the exact series of the wafer fabrication process are carried out to verify the consistency of the electrical performance and the hypothesis that made earlier from the TCAD simulation.

Besides non-destructive analysis, we also perform ESD surge test as the destructive analysis to validate the hypothesis and the impact of the process changes as well.

rotected

#### **1.5 Thesis Organization**

The thesis has covered the simulation, wafer fabrication and characterization of the P-i-N power switching diode. Chapter 1 brings an insight of research to the audience. The fundamentals and also evolution of power switching diode are discussed in literature review section Chapter 2. Besides fundamental theory, the application of power switching diode is discussed too.

Chapter 3 has demonstrated the process flow of designing the experiments and also power switching diode wafer fabrication process. Device characterization test after fabrication is also discussed in this chapter. There are two types of device characterization test, the destructive and the non-destructive. Characterization test carry the purpose to test