# Two dimensional simulation and analysis of density-of-states (DOS) in top-gated nanocrystalline silicon thin film transistor (nc-Si TFT)

Prachi Sharma<sup>1</sup> and Navneet Gupta<sup>2</sup>

<sup>1,2</sup>Department of Electrical & Electronics Engineering, Birla Institute of Technology and Science, Pilani, Rajasthan, India

Received 1 Jan 2017; Revised 23 Mar 2017; Accepted 6 Apr 2017

#### **Abstract**

In this paper, we have presented the effect of the density-of-states (DOS) parameters on the performance of n-channel top gated staggered nc-Si TFT. The analysis was performed using ATLAS 2D TCAD simulator from SILVACO. The variation in DOS in nc-Si material and thus on the TFT device performance occurred by altering the channel length and channel quality is presented. The simulation results reveal that the increase in channel length and the degradation in channel quality degrade the trans-conductance and drain current. By iterating the order of parasitic resistance and the value of characteristic decay energy related to material quality, the same trend is achieved for simulated and experimental results for nc-Si TFT with  $W/L=200\mu m/50\mu m$ .

**Keywords**: Nanocrystalline silicon; Thin film transistor; TCAD; ATLAS; Channel length; Density of states.

### 1. Introduction

The nanocrystalline silicon (nc-Si) has several advantageous features including enhanced mobility [1] and better stability [2, 3] over amorphous silicon (a-Si) and it also provide structural uniformity and low fabrication cost [4] when compared with polycrystalline silicon (poly-Si) [5-11]. Therefore nc-Si has received huge attention to be used as thin film transistor (TFT) channel layer in various display applications like active matrix organic light emitting diode (AMOLED) [12], medical X-ray imagers [13] and radio frequency identification devices (RFID) tags [14]. Based on the level of the gate electrode, the TFTs are divided into two types; top gated TFT and bottom gated or inverted TFT. In top gate TFT, the gate electrode is located above the semiconductor layer, whereas in bottom gate TFT, the gate electrode is located below the semiconductor layer.

Limited papers have been published based on the numerical simulation of nc-Si TFT [15-17] Dosev et. al. [15] provided the numerical simulation results for inverted staggered TFTs using SiO2 dielectric and presented the influence of acceptor-like defect states density on transconductance. They examined that the acceptor-like defect states in nc-Si:H are filled at much lower gate voltages than in a-Si:H TFTs having similar threshold voltages. The transconductance shape of nc-Si:H TFTs has a shape typical for a-Si:H TFTs before the

<sup>\*)</sup> For Correspondence. E-mail: prachi.sharma@pilani.bits-pilani.ac.in, ngupta@pilani.bits-pilani.ac.in

acceptor-like states are filled. When electrons fill the acceptor-like states, the transconductance of nc-Si:H TFTs become typical for poly-Si TFTs. The reason for this behavior is the density of acceptor-like states, which situates the nc-Si:H TFTs properties between a-Si:H and the poly-Si transistors. However, authors [15] considered an optical gap of 1.91 eV which is not a normal value neither for a-Si:H nor for nc-Si:H devices. For devices with a gap of 1.72 eV, M. Estrada et. al. [16] demonstrated that the anomalous effect of the transconductance is related to the trapped charge concentration characteristics and observed that the acceptor tail states activation energy is similar to the normal values for a-Si devices of 0.035eV, provided that some conditions are met regarded the concentration of trapped charges in tail and deep states and the free charge concentration in the material, which doesn't necessarily suggest a behavior in between a-Si:H and poly-Si. Archontas et.al. [17] proposed the electrical behavior of inverted staggered TFTs using Si3N4 as gate dielectric and presented the transfer and output characteristic of inverted staggered nc-Si TFTs with different channel lengths. They have found that in the off-state region, the conduction mechanism at less negative gate voltages was attributed to thermal generation while in case of high negative gate voltages (<-15 V), the leakage current was due to the band to band tunneling mechanism.

When the nc-Si:H film is deposited over the amorphous substrate like glass, then its crystallinity is not very high in the initial growth phases because the nc-Si:H is usually grown up in the form of cone-shape that is from bottom to top. The crystallinity increases with the increase in nc-Si:H film thickness [18] This structural difference in top and bottom layers of nc-Si:H film plays crucial role in designing nc-Si:H TFT. In the case of bottom-gate structure, the device performance depends on the bottom layer of nc-Si:H film where the channel is formed as compared to top-gate TFT, where the channel is located in highly crystalline part at the top of nc-Si:H film [19]. Owing to this, the top-gate nc-Si:H TFT provides high field effect mobility ( $\mu$ FET) i.e. in range of 40 cm2/Vs [20] to 150 cm2/Vs [7] as compared to bottom-gate TFT which have  $\mu$ FET as 0.5-3 cm2/Vs [21, 22] Therefore, in this paper we have presented the numerical simulation of top-gate staggered nc-Si TFT at various channel lengths and characteristics of decay energy which has not been explored by other research groups [15-17] .

In the present work, for the device simulation of top-gate nc-Si TFT, the high-k gate dielectric i.e. Si3N4 is considered in place of SiO2 because Si3N4 shows high capacitance densities with wider tunneling barrier, high breakdown field and less interface trap density as compared to SiO2 and hence provide better electrical stability in nc-Si TFT [23].

## 2. Theory and Model

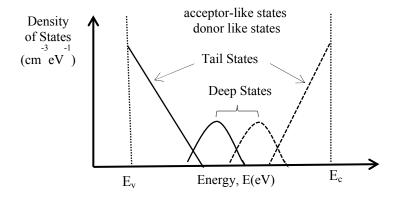

Hot wire chemical vapour deposition (HWCVD) method is commonly used for the deposition of nc-Si:H over glass substrate. The resulting nc-Si:H film consists of small silicon crystallites than poly-Si, with an average grain size of a few nanometers, embedded into a-Si:H. It provides the possibility of direct deposition of nc-Si:H at a very low temperature over a large area and at high deposition rates [24]. However, the low temperature process used for nc-Si deposition as well as the amorphous nature of noncrystalline substrate (like glass) lead to the formation of material having missing atoms. Deep defect states in the forbidden energy gap of the nc-Si are associated with these missing atoms, i.e. dangling bonds [25]. Deep defect states are also associated with the deviation in bond length and angle which results in states below the conduction band, known as band tail states [26]. DOS in nc-Si (as depicted in Figure 1) is composed of two Gaussian distributed deep defect states (acceptor-like and donor-like deep states) and two exponentially distributed band tail states (acceptor-like and donor-like tail states). The density of states

that are presented in the upper half region of the band gap acts as the acceptor like states whereas the states that are in the bottom half region of the band gap acts as the donor-like states. The acceptor-like states are negatively charged when they are occupied and neutral when they are unoccupied. However, the donor-like states are positively charged when they are unoccupied and neutral when they are occupied [27].

Figure 1: Density of states within the band gap of nc-Si

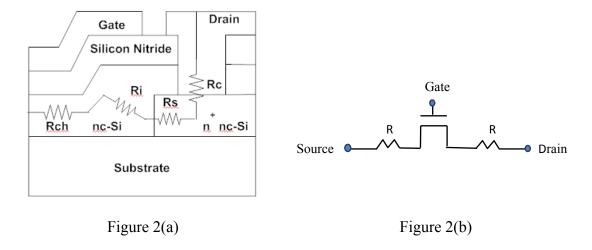

DOS in nc-Si TFT is highly influenced by the parasitic resistance associated with the geometrical aspects like channel length [28,29,17] and also by the quality of channel layer [15]. Parasitic resistance component, R in n-channel top gated staggered TFT as shown in Figure 2 consists of series resistance of active layer (Rch) and insulating layer (Ri), series resistance of contact layers (Rs) and contact resistance (Rc) between metal electrode and source/drain contacts, given by:

$$R = R_{ch} + R_i + R_s + R_c \tag{1}$$

Therefore, parasitic resistance can strongly influence the transconductance and drain current of the TFT device. Therefore, deepe investigation of parasitic resistance is required for the further enhancement of TFT performance.

Figure 2: (a) Parasitic resistance (R) components of the n-channel top gated nc-Si TFT and (b) Equivalent circuit of the TFTs used for device simulation

DOS model, which is available in TFT module in ATLAS tool package, is used to extract the density of states present in the band gap of nc-Si. We have considered the case that DOS has a continuous distribution from the band tail states to the extended energy states. DOS can be defined as a function of energy as follows:

$$g(E) = g_{GA}(E) + g_{GD}(E) + g_{TA}(E) + g_{TD}(E)$$

(2)

Where

$$g_{GA}(E) + g_{GD}(E) + g_{TA}(E) + g_{TD}(E)$$

$$g_{GA}(E) = NGA \exp\left[-\left(\frac{EGA - E}{WGA}\right)^{2}\right]$$

$$g_{GD}(E) = NGD \exp\left[-\left(\frac{E - EGD}{WGD}\right)^{2}\right]$$

$$g_{TA}(E) = NTA \exp\left(\frac{E - E_{C}}{WTA}\right)$$

$$g_{TD}(E) = NTD \exp\left(\frac{E_{V} - E}{WTD}\right)$$

(6)

$$g_{GD}(E) = NGD \exp\left[-\left(\frac{E - EGD}{WGD}\right)^2\right]$$

(4)

$$g_{TA}(E) = NTA \exp\left(\frac{E - E_C}{WTA}\right)$$

(5)

$$g_{TD}(E) = NTD \exp\left(\frac{E_V - E}{WTD}\right)$$

(6)

where  $E_C$  and  $E_V$  are the conduction and valence band edge energies, E is the trap energy, N is the edge intercept density, W is the characteristic decay energy and the subscripts (T, G, G)A, D) stand for band tail, Gaussian deep, acceptor and donor states respectively.

#### 3. Simulation and Analysis

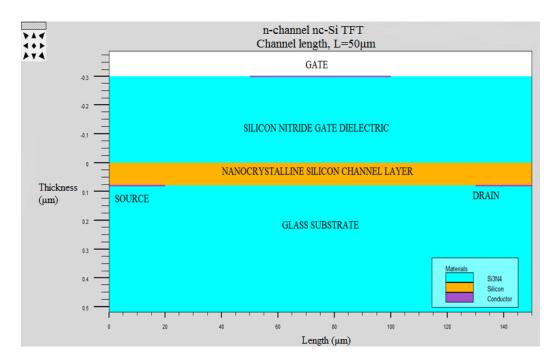

Figure 3 shows the virtually fabricated TFT structure used for 2D device simulation on ATLAS by SILVACO. Table 1 shows the value of various nc-Si TFT parameters used for device simulation.

Figure 3: nc-Si TFT structure for ATLAS simulation

The nc-Si is used as an active layer with a thickness of 80 nm and the 300 nm thick Si<sub>3</sub>N<sub>4</sub> layer is used as a gate dielectric. The width of the device is taken as 200µm and the device length range varies from 50µm to 90µm. The drain voltage, V<sub>DS</sub> is fixed at 10V. In spite of defining a new layer, the source and drain regions are implemented using highly doped (i.e.  $10^{20}$  /cm<sup>3</sup>) n+ region and the aluminum metal contact on the top of it. The parasitic resistance is employed as a lumped component in the simulation input desk separately and is not defined in the mesh structure.

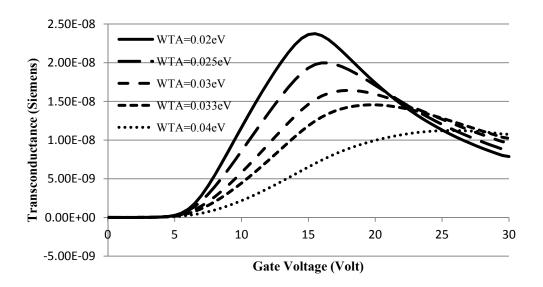

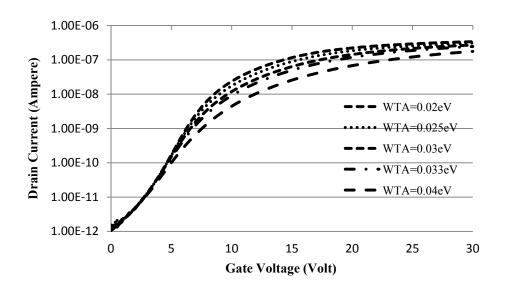

The influence of DOS (i.e. the nc-Si material properties) on the nc-Si TFT performance is investigated by considering different values of characteristic decay energy (WTA) as 0.020, 0.025, 0.033, 0.030, 0.040 eV and keeping parasitic resistance value fixed at  $10^6 \Omega$ . The higher value of WTA relates to the wider acceptor like tail states, which corresponds to the film, which has more amorphous-like properties and thus higher parasitic resistance. Similarly, the lower value of WTA defines that the film is more polycrystalline.

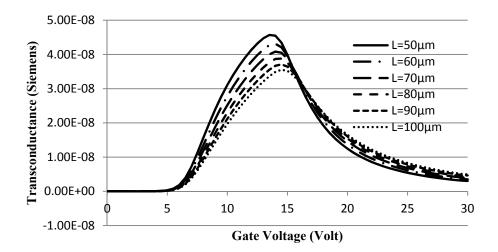

The simulation results reveal that the transconductance degradation (as shown in Figure 4) occurs as the film become more amorphous or as the value of WTA increases from 0.020 to 0.040eV. This transconductance degradation due to the variation in material quality causes the reduction of drain current as illustrated in Figure 5 and thus limits the oncurrent of a device.

Figure 4: Variation of transconductance as a function of gate voltage for different values of tail states

Figure 5: Variation of drain current as a function of gate voltage for different values of tail states

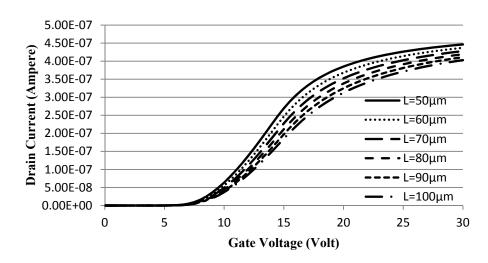

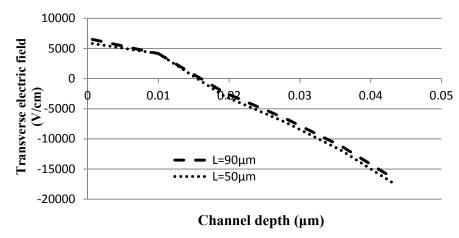

The channel length dependence on the drain current of nc-Si TFT is analyzed by varying the channel length from 50 to  $100\mu m$  while maintaining other parameter like DOS as fixed at initial fitting values (i.e. WTA=0.02eV). The simulation results indicate that an increase in channel length degrades the transconductance as shown in Figure 6 and hence the drain current as shown in Figure 7. This drain current degradation is attributed due to the increase in overall parasitic resistance due to the increase in weight of the series resistance of the channel layer. The drain current degradation can also be explained by the increase of the transverse electric field on increasing the channel length even if the channel depth remains fixed. This variation is illustrated in Figure 8 for the channel length values of  $50\mu m$  and  $90\mu m$ .

Figure 6: Variation of transconductance as a function of gate voltage for different values of channel length

Figure 7: Variation of drain current as a function of gate voltage for different values of channel length

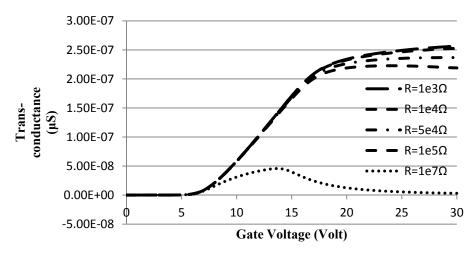

The dependence of parasitic resistance on the transconductance is analyzed by varying the parasitic resistance, R from  $10^3$  to  $10^7$   $\Omega$  and considering the fixed value of WTA as 0.02eV. The simulation result shown in Figure 9 reveals that the transconductance decreases as the parasitic resistance increases from  $10^3$  to  $10^7$   $\Omega$ . This increase in R value is

due to the increase in the series resistance of the channel layer with the increase in channel length.

Figure 8: Channel length dependence on Transverse electric field

Figure 9: Variation of transconductance as a function of gate voltage for different values of parasitic resistance

Table 1: ATLAS device simulation parameter for nc-Si TFT

| Parameter | Description                                                    | nc-Si            |

|-----------|----------------------------------------------------------------|------------------|

| NTA       | Conduction band edge intercept tail states density             | 1x10 cm          |

| NTD       | Valence band edge intercept tail states density                | $1x10^{20}$ cm   |

| NGA       | Conduction band edge intercept deep states density             | $3.7x10^{17}$ cm |

| NGD       | Valence band edge intercept deep states density                | $3.7x10^{17}$ cm |

| EGA       | Peak energy of deep states as E=E <sub>C</sub>                 | 0.4 eV           |

| EGD       | Peak energy of deep states as E=E <sub>V</sub>                 | 0.4 eV           |

| WTA       | Characteristic decay energy of tail states as E=E <sub>C</sub> | 0.025 eV         |

| WTD       | Characteristic decay energy of tail states as E=E <sub>v</sub> | 0.025 eV         |

| WGA       | Characteristic decay energy of deep states as E=E <sub>C</sub> | 0.1 eV           |

| WGD       | Characteristic decay energy of deep states as E=E <sub>v</sub> | 0.1 eV           |

Figure 10 shows the comparison between simulated and experimental results of Lee at. al. [30]. In simulation, the value for WTA and R is kept fixed at 0.02eV and  $10^6~\Omega$ , respectively. In order to compare the simulated results with the experimental findings, a modeling factor N=exp( $\alpha$ ) is used where the value of  $\alpha$  is taken as 0.27. This factor will compensate the difference between the simulated DOS value and actual DOS in nc-Si film used in device fabrication. The simulated drain current results show similar trends with experimental variation. However, the deviation from the experimental results is attributed due to the fact that the experimentally fabricated device may have different DOS value due to different nc-Si material quality.

Figure 10: Plot of the transfer characteristic of nc-Si top-gated TFT (W=200 $\mu$ m and L=50 $\mu$ m) simulated at V<sub>DS</sub>=10V for WTA=0.02 and R=10<sup>6</sup>  $\Omega$ . Solid line shows the experimental results of C.H.Lee et. al. [30] and dotted line shows simulated results

#### 4. Conclusion

The effects of DOS and channel length on the performance of nc-Si TFT has been investigated using ATLAS 2D device simulator by SILVACO. The simulation results reveal that the channel material properties affect the device transconductance due to the increase in the value of characteristic decay energy. This causes the increase in DOS and therefore degrades the drain current which in turn limits the on-state device performance. It has been also observed that the increase in channel length also degrades the transconductance and drain current due to increase in weight of parasitic resistance. The outcome of this study is compared with the experimental data and the similar trend between the two has been observed.

#### Acknowledgments

We would like to acknowledge CSIR-HRDG for providing Senior Research Fellowship (SRF) as financial support.

### References

[1] Abhishek Mukherjee, Prachi Sharma and Navneet Gupta, "Modeling of Field Effect Mobility using Grain Boundaries on Nanocrystalline Silicon Thin-Film Transistor (nc-Si TFT)" Journal of Nano- and Electronic Physics, 04054-1-3 (5), 2013

- [2] Prachi Sharma and Navneet Gupta, "Model for threshold voltage instability in top-gated nanocrystalline silicon thin film transistor" Journal of Computational Electronics (Springer), 666-671(15) 2, 2016

- [3] Prachi Sharma and Navneet Gupta, "Threshold Voltage Modeling on Nanocrystalline Silicon Thin-Film Transistors", Journal of Electron Devices, 1608-1612 (19) 2014

- [4] Prachi Sharma, Nishant Tripathi and Navneet Gupta, "Nanocrystalline silicon thin film prepared by e-beam evaporation for display application" Journal of Materials Science: Materials in Electronics (Springer), 3891–3896 (28) 4, 2017

- [5] Shin K. W., Fabrication and Analysis of Bottom Gate Nanocrystalline Silicon Thin Film Transistors [PhD thesis], University of Waterloo, Canada, 2008

- [6] Cheng I. C., Allen S., Wagner S. "Evolution of Nanocrystalline Silicon Thin Film Transistor Channel Layers" Proceedings of the 20th International Conference on Amorphous and Microcrystalline Semiconductors, Campos do Jordao, Brazil, 2003, August 24-29, 720-724

- [7] Lee C. H., Sazonov A., Nathan A. "High-mobility nanocrystalline silicon thin-film transistors fabricated by plasma-enhanced chemical vapor deposition" *Applied Physics Letters*. 2005, 86: 222106-1-3

- [8] Hatzopoulos A. T., Arpatzanis N., Tassis D. H., Dimitriadis C. A., Templier F., Oudwan M., Kamarinos G. "Effect of channel width on the electrical characteristics of amorphous/nanocrystalline silicon bilayer thin-film transistors" *IEEE Transaction on Electron Devices*. 2007, 54: 1265-1269

- [9] Kasouit S., Cabarrocas P. R. I., Vanderhaghen R., Bonnassieux Y., Elyaakoubi M., French I. D. "Effects of Grain Size and Plasma-Induced Modification of the Dielectric on the Mobility and Stability of Bottom Gate Microcrystalline Silicon TFTs" Proceedings of the 20th International Conference on Amorphous and Microcrystalline Semiconductors, Campos do Jordao, Brazil, 2003, August 24-29, 369-373

- [10] Kuo Y. "Thin Film Transistors: Materials and Process" 2<sup>nd</sup> vol., 1<sup>st</sup> ed., Kluwer Academic, New York, USA, 2004, 120-126

- [11] Gupta N, and Tyagi B. P. "On-current modeling of polycrystalline silicon thin-film transistors." *Physica Scripta*. 2005, 72: 339-342.

- [12] Snell A. J., Mackenzie K. D., Spear W.E., Le Comber P. G. "Application of amorphous silicon field effect transistors in addressable liquid crystal display panels" *Applied Physics Letter*. 1981, 24: 357-362

- [13] Street R. A. "Technology and Applications of Amorphous Silicon" Springer, Berlin Heidelberg, New York. 2000

- [14] Finkenzeller K. "RFID Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification" 2nd ed. John Wiley & Sons. Ltd., West Sussex, England. 2003

- [15] Dosev D., Iniguez B., Marsal L. F., Pallares J., Ytterdal T. "Device simulations of nanocrystalline silicon thin-film transistors" *Solid-State Electronics*. 2003, 47:1917-1920

- [16] Estrada M., Cerdeira A., Resendiz L., Iniguez B., Marzal L. F, Pallares J. "Effect of localized traps on the anomalous behavior of the transconductance in nanocrystalline TFTs" *Microelectronics Reliability*. 2005, 45: 1161–1166

- [17] Archontas N., Georgoulas N., Dimitriadis C. A., Templier F., Oudwan M. and Kmarinos G. "Two dimensional simulation and modeling of the electrical behavior in nanocrystalline silicon thin-film transistors" Journal of Applied Physics. 2008, 103:1045071-1045077

- [18] Park J.H., Han S.M., Choi Y.H., Kim S.J., Han M.K., "New In-Situ Process of Top Gate Nanocrystalline Silicon Thin Film Transistors Fabricated at 180° C for the Suppression of Leakage Current," IEEE International Electron Devices Meeting, Washington, 2007, Dec 10-12, 595-598

- [19] Esmaeili-Rad M. R., *Nanocrystalline Silicon Thin Film Transistor* [PhD thesis], University of Waterloo, Canada, 2008

- [20] Cheng I. C., Allen S., Wagner S. "Evolution of Nanocrystalline Silicon Thin Film Transistor Channel Layers" Proceedings of the 20th International Conference on Amorphous and Microcrystalline Semiconductors, Campos do Jordao, Brazil, 2003, August 24-29, 720-724

- [21] Hatzopoulos A. T., Arpatzanis N., Tassis D. H., Dimitriadis C. A., Templier F., Oudwan M., Kamarinos G. "Effect of channel width on the electrical characteristics of amorphous/nanocrystalline silicon bilayer thin-film transistors" *IEEE Transaction on Electron Devices*. 2007, 54: 1265-1269

- [22] Kasouit S., Cabarrocas P. R. I., Vanderhaghen R., Bonnassieux Y., Elyaakoubi M., French I. D. "Effects of Grain Size and Plasma-Induced Modification of the Dielectric on the Mobility and Stability of Bottom Gate Microcrystalline Silicon TFTs" Proceedings of the 20th International Conference on Amorphous and Microcrystalline Semiconductors, Campos do Jordao, Brazil, 2003, August 24-29, 369-373

- [23] Sharma P and Gupta N. "Investigation on material selection for gate dielectric in nanocrystalline silicon (nc-Si) top-gated thin film transistor (TFT) using Ashby's, VIKOR and TOPSIS" 2015, DOI- 10.1007/s10854-015-3624-9

- [24] Kuo Y. "Thin Film Transistors: Materials and Process" 2<sup>nd</sup> vol., 1<sup>st</sup> ed., Kluwer Academic, New York, USA, 2004, 120-126

- [25] Greve D. W., "Field Effect Devices and Applications: Devices for Portable, Low-Power, and Imaging Systems", Prentice-Hall, Englewood Cliffs, NJ, 1998

- [26] Street R. A. "Hydrogenated Amorphous Silicon", Cambridge University Press, Cambridge, 1991.

- [27] M. Shur, Physics of Semiconductor Devices. New Jersey: Prentice Hall, Inc., 1990

- [28] Ahmad, S. "Device applications of band-structure-engineered nanomaterials current status and future trend-review", International Journal of Nanoelectronics and Materials, **8**, pp. 129-202, 2015

- [29] Chaudhry A and Roy J. N. "Analytical modeling of energy quantization effects in nanoscale mosfets" International Journal of Nanoelectronics and Materials, 5, pp.1-9, 2012

- [30] Lee, C. H., Striakhilev, D. and Nathan, A. "Stability of nc-Si: H TFTs with silicon nitride gate dielectric" IEEE Transactions on Electron Devices. 2007, 54:45-51