### **Universiti Malaysia Perlis**

#### INVENTORS

DR. MOHD KHAIRUDDIN MD ARSHAD PROF. DR. UDA HASHIM NORAINI OTHMAN

#### CONTACT DETAILS

INSTITUTE OF NAND ELECTRONIC ENGINEERING (INEE)

UNIVERSITI MALAYSIA PERLIS

01000 KANGAR, PERLIS

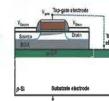

## **ASYMMETRICAL DOUBLE GATE:** SIGNIFICANT IMPROVEMENT IN **ULTRA-SCALED SOI MOSFET**

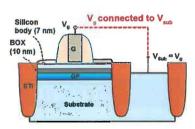

# body (7 nm) V<sub>Sub</sub> = V<sub>p</sub> Substrate

AVSIA PENLIS

#### INTRODUCTION

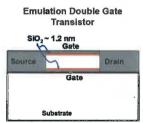

Fully-depletion operation is mandatory requirement for ultra-scaled devices (i.e. < 45 nm technology) which only can be achieved either multi-gate (i.e. FinFET) or thin body Silicon-on-Insulator (SOI). Thin body SOI offers another interesting feature compared to any other technologies i.e. back-gate biasing. In this invention, we utilize asymmetrical contact from the top which provide improved performance and better controlled of short-channel effects in thin body and thin buried oxide of SOI MOSFETs.

Elimination Short Channel Smaller **Effects**

**Short Channel Effects**

#### NOVELTY

**Existing Technologies**

#### **New Invention**

Ground

Planar Architecture - Silicon

3D Architecture - Silicon/ SOI Platform

Planar Architecture - SOI Platform

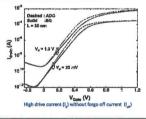

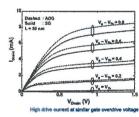

- · Simple architecture with significant Improvement on drive current (Id-Vg and Id-Vd) without forgo the off current.

- Extension to ultra-scaled devices: support Moore's Law for ~ 10 nm technology

- Eliminate Short Channel Effects

#### Collaboration

- · Université catholique de Louvain, Louvain-la-neuve, Belgium

- CEA Leti, Grenoble, France

Arshad et al, Solid-State Electronics, 2014 (accepted for publication) had et al. Solid-State Electronics, 90, 2013; 56-64 nl. IEEE Trans. Electron Devices, 59, 2012: 247-251 actronics, 71, 2012: 93-100

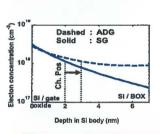

#### RESULTS

#### **I-V Characteristics**

#### COMMERCIALIZATION POTENTIAL

| 22 nm gate length   | Single<br>Gate | Asymmetrical Double Gate | % improvement |

|---------------------|----------------|--------------------------|---------------|

| V <sub>Th</sub> (V) | 0.45           | 0.30                     | 30 %          |

| SS (mV/dec)         | 95             | 80                       | 15 %          |

| DIBL (mV/V)         | 115            | 95                       | 18 %          |

| Ion (uA/um)         | 500            | 620                      | 24 %          |

- · Lower threshold voltage (i.e suitable for low power application -energy saving)

- · Lower subthreshold slope (i.e faster switching speed between on and off).

- · Lower drain-induced barrier lowering (i.e. better control of short channel effects : translated into ~ 20 % increased in speed.

#### PRODUCT IMPLEMENTATION

Low power mobile application i.e. smart phone.