#### **CHAPTER 4**

### **RESULTS & DISCUSSION**

#### 3.2 Introduction

This project aims to prove that Modified Baugh-Wooley Two's Complement Signed Multiplier is one of the high speed multipliers. The schematic of the multiplier is designed and analyzed using Block Design Editor that is provided in Altera's Quartus II Software. In order to check the speed performance, the schematic is analyze using Timing Analyzer Tool. The multiplier consists of AND gate, NAND gate, Half Adder, Carry Save Adder and D flip-flop. This chapter will discuss about the design that has been made for 8-bits x 8-bits Modified Baugh-Wooley Two's Complement Signed Multiplier and the results achieved.

#### 4.2 Half Adder

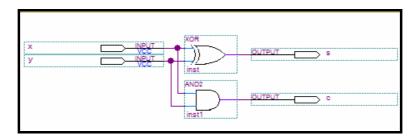

Half Adder is an arithmetic circuit that generates the sum of two binary digits. It has two inputs and outputs. The Half Adder is implemented with one exclusive OR gate and one AND gate as shown in Figure 4.1.

Figure 4.1 : Logic Diagram of Half Adder

The result for this Half Adder is shown in Figure 4.2. The result of this Half Adder is exactly the same as in Table 3.3 that has been explained in Section 3.3.3.

| Mas | ter Time 4 | 0.0 ns 🔸 Poir       | nter 3.6 ns | Interval -36.4 ns St | tart End |

|-----|------------|---------------------|-------------|----------------------|----------|

|     | Name       | Value at<br>40.0 ns | 0 ps        | 10.0 ns              | 20.0 ns  |

|     | x          | BO                  |             |                      |          |

|     | У          | B 0                 |             |                      |          |

| •   | с          | В 0                 |             | [                    |          |

| •   | s          | B 0                 |             |                      |          |

|     |            |                     |             |                      |          |

Figure 4.2 : Simulation Waveform of Half Adder

## 4.3 Carry Save Adder

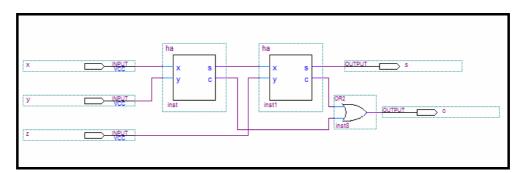

Carry Save Adder accepts three n-bit operands and generates two n-bit results, an n bit partial sum, and n-bit carry. As shown in Figure 4.3, the logic diagram for Carry Save Adder consists of two Half Adder blocks and an OR gate. Half Adder block is created from Half Adder.bdf file using Create Symbol Tool.

Figure 4.3 : Logic Diagram of Carry Save Adder

The result of Carry Save Adder in shown in Figure 4.4. It shows that the result is exactly the same with Table 3.4 in Section 3.3.4.

| Masl | ter Time Bar: | 0 ps             | <ul> <li>Pointer:</li> </ul> | 19.9 ns | Interval: 19.9 ns | Start:  | End:    |

|------|---------------|------------------|------------------------------|---------|-------------------|---------|---------|

|      | Name          | Value at<br>0 ps | 0 ps<br>0 ps                 | 10.0 ns | 20.0 ns           | 30.0 ns | 40.0 ns |

| Â    | ×             | B 0              |                              |         |                   |         |         |

|      | У             | B 0              |                              |         |                   |         |         |

|      | z             | B 0              |                              |         |                   |         |         |

| 0    | s             | B 0              |                              |         |                   |         |         |

| 6    | с             | B 0              |                              |         |                   |         |         |

|      |               |                  |                              |         |                   |         |         |

Figure 4.4 : Simulation Waveform of Carry Save Adder

# 4.4 Modified Baugh-Wooley Two's Complement Signed Multiplier

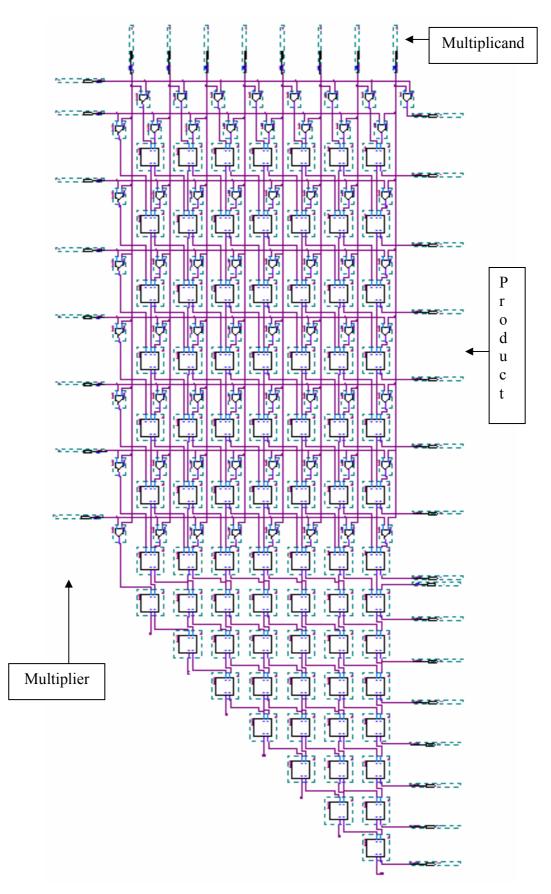

The design of 8-bits x 8-bits Modified Baugh-Wooley Two's Complement Signed Multiplier is done by referring to the tabular form of bit-level Modified Baugh-Wooley multiplication. The implementation of this circuit needed AND gates, NOT gates, Half Adders and Carry Save Adders to form the partial product bits as shown in Figure 4.5 in next page.

Figure 4.5: 8-bits x 8-bits Modified Baugh-Wooley Two's Complement Signed Multiplier

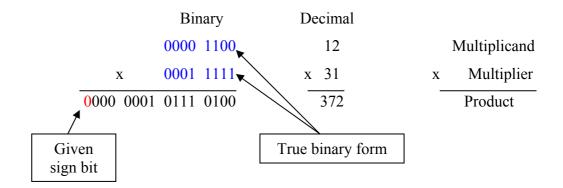

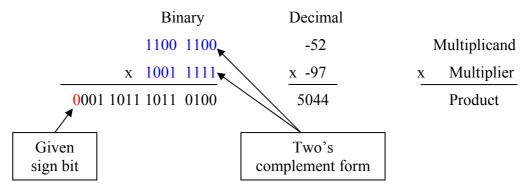

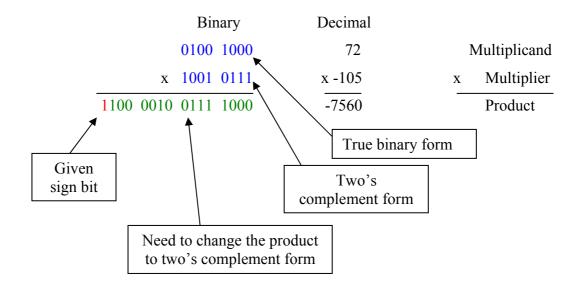

Modified Baugh-Wooley Two's Complement Signed Multiplier is a two's complement parallel array multiplier. Since it uses two's complement representation, the multiplicand and the multiplier are put in true binary form to perform multiplication. If the two numbers to be multiplied are positive, both are already in true binary form and are multiplied as they are. The resulting product is positive and is given a sign bit of 0.

Figure 4.6 shows the correct answer of multiplication for the two positive numbers. The result is represented in binary and decimal numbering system verification. Since the range of positive numbers in an 8-bit system is 0000 0000 to 0111 1111 (0 to 127), only selected number are displayed.

|            | ime Bar: | 0 ps              | <ul> <li>Pointer:</li> </ul> | 69.5 ns Interv    | val: 69.5 ns      | Start:            | End:              |                   |  |  |

|------------|----------|-------------------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|--|

|            | Mana     | 0 ps 10.<br>0 ps  | Dins 20.                     | 0 ns 30.          | Ons 40.           | 0 ns 50.          | Dins 60.          | ) ns 70.0 ns      |  |  |

| _          |          | ]                 |                              |                   |                   |                   |                   |                   |  |  |

|            | 1<br>Bla |                   | (12)                         | (24)              | (36)              | (48)              | 60                | 72                |  |  |

|            | E b      | 7                 | (31)                         | (55)              | (79)              | (103)             | 127               | -105              |  |  |

| <b>(</b> ) | Вр       |                   | 372                          | (1320)            | 2844              | 4944              | 7620              | -7560             |  |  |

|            | a        | 0000000           | ( 00001100 )                 | ( 00011000 )      | ( 00100100 )      | ( 00110000 )      | ( 00111100 )      | 01001000          |  |  |

| <b>P</b>   | E b      | 00000111          | ( 00011111 )                 | ( 00110111 )      | ( 01001111 )      | ( 01100111 )      | ( 01111111 )      | 10010111          |  |  |

| <b>@</b>   | E p      | (000000000000000) | (000000101110100)            | (000010100101000) | (000101100011100) | (001001101010000) | (001110111000100) | (110001001111000) |  |  |

Figure 4.6 : Simulation Waveform of Both Positive Numbers Multiplication

When two numbers are negative, it will be in two's complement form. The two's complement of each is taken to convert it to a positive number, and then the two numbers are multiplied. The product is kept as a positive number and is given a sign bit of 0.

Figure 4.7 shows the correct answer of multiplication for the two negative numbers. The result is represented in binary and decimal numbering system verification. The range of negative numbers is 1111 1111 to 1000 0000 (-1 to -128), only selected number are displayed.

| Master Time Bar: |      | Ops 🔸            | Pointer: 209.5 r  | ns Interval:      | 209.5 ns Start: | Enc               | :                  |  |  |

|------------------|------|------------------|-------------------|-------------------|-----------------|-------------------|--------------------|--|--|

|                  | Name | 160.0 ns 170     | 0 ns 180          | 0 ns 190          | 0 ns 200        | 0 ns 210          | 0 ns 220.0 ns      |  |  |

|                  | Name |                  |                   |                   |                 |                   |                    |  |  |

|                  | 1    |                  |                   |                   |                 |                   |                    |  |  |

| 3                | ± a  | -64              | (-52)             | (-40              | -28             | (-16              | (-4)               |  |  |

| <b></b>          | ± b  | -121             | (-97)             | (-73              | (-49            | -25               | (-1)               |  |  |

| 1                | ±ρ   | (7744)           | (5044)            | ( 2920            | 1372            | ( 400 )           | ( 4                |  |  |

| 3                | ± a  | ( 11000000 )     | ( 11001100 )      | ( 11011000 )      | 11100100        | ( 11110000 )      | ( 11111100 )       |  |  |

| 3                | ±ь   | ( 10000111 )     | ( 10011111 )      | ( 10110111 )      | 11001111        | ( 11100111 )      | ( 11111111 )       |  |  |

| 1                | ±р   | (00111100100000) | (001001110110100) | (000101101101000) | 000010101011100 | (000000110010000) | (0000000000000000) |  |  |

|                  |      |                  |                   |                   |                 |                   |                    |  |  |

Figure 4.7 : Simulation Waveform of Both Negative Numbers Multiplication

When one of the numbers is positive and the other is negative, the negative number is first converted to a positive magnitude by taking its two's complement. The product will be in true magnitude form. However, the product must be negative, since the original numbers are of opposite sign. Thus, the product is then changed to two's complement form and is given a sign bit of 1.

Figure 4.8 shows the result for positive and negative numbers multiplication. The results of multiplications for both numbers are correct. Only selected numbers are displayed, due to the wide range of numbers that can be multiplied together.

| Mas | ter Time Bar: | O ps 🔹 🕨          | Pointer: 125.9 r  | ns Interval:      | 125.9 ns Start:   | En                | d:               |

|-----|---------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|     |               | 60.0 ns 70.       | 0 ns 80.          | 0 ns 90.          | 0 ns 100          | 0 ns 110          | .0 ns 120.0 n    |

|     | Name          |                   |                   |                   |                   |                   |                  |

|     | 1             |                   |                   |                   |                   |                   |                  |

|     | 🛨 a           | 72                | (84)              | 96                | ( 108             | 120               | ( -124           |

| ľ   | Ξb            | -105              | (-81)             | -57               | (-33              | (-9               | (15              |

| ß   | ±р            | -7560             | -6804             | -5472             | -3564             | -1080             | -1860            |

|     | ± a           | 01001000          | 01010100          | 01100000          | 01101100          | 01111000          | 10000100         |

| 3   | ⊞ b           | 10010111          | ( 10101111 )      | 11000111          | 11011111          | 11110111          | 00001111         |

|     | ±р            | (110001001111000) | (110010101101100) | (110101010100000) | (111001000010100) | (111101111001000) | (111100010111100 |

|     |               |                   |                   |                   |                   |                   |                  |

Figure 4.8 : Simulation Waveform of Positive and Negative Numbers Multiplication

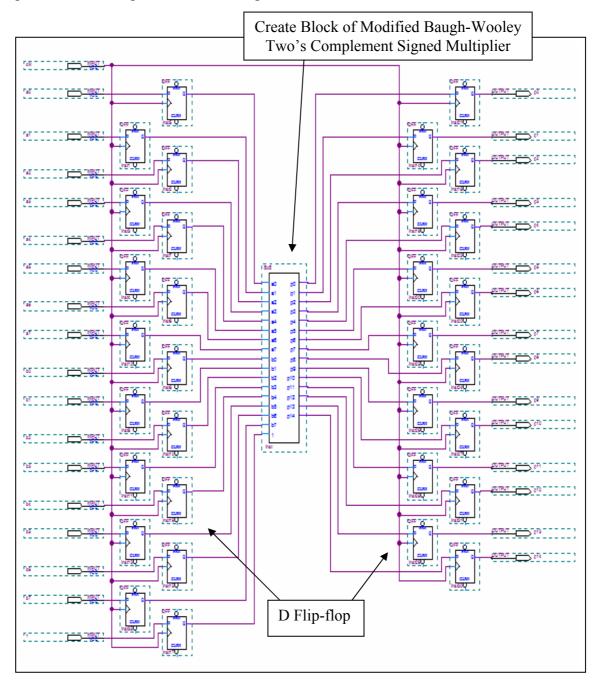

The main objective for this project is to prove that Modified Baugh-Wooley Two's Complement Signed Multiplier is a high speed multiplier. In order to check the speed performance, D Flip-flop must be connected first to each inputs and outputs to provide a clock signal as shown in Figure 4.9.

**Figure 4.9** : 8-bit x 8-bit Modified Baugh-Wooley Multiplier with D Flip-flop at inputs and outputs

The speed value for this multiplier is 20.33MHz as shown in Figure 4.10.

| Registered Per | formance  | tpd | tsu                  | tco   | th                | Custom Delays |

|----------------|-----------|-----|----------------------|-------|-------------------|---------------|

| Clock: clk     |           |     |                      |       |                   |               |

|                | Value     |     |                      |       |                   |               |

| From           | inst8     |     |                      |       |                   |               |

| То             | inst30    |     |                      |       |                   |               |

| Clock period   | 49.200 ns |     |                      |       |                   |               |

| Frequency      | 20.33 MH  | z   |                      |       |                   |               |

|                |           |     | 10<br>75<br>50<br>25 | 0 125 | 150<br>17:<br>22: | 00            |

Figure 4.10 : Speed Performance for Modified Baugh-Wooley Multiplier

The output from this multiplier is shown in Figure 4.11. The multiplication results for this multiplier are correct. It should be noted that, there is delay for first output that been introduced by D Flip-flop registers.

| Mas | ter Time Bar: |          | ps  Pointer: 105.6 ns Interval: 105.6 ns Start: End:                                                                              |    |

|-----|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|     | Name          | Value at | 0.ps 10.0 ns 20.0 ns 30.0 ns 40.0 ns 50.0 ns 60.0 ns 70.0 ns 80.0 ns 90.0 ns 100,0 ns 110,0 ns 120,0 ns 130,0 ns 140,0 ns 15<br>n | 0, |

|     | Hamo          | 0 ps     | Ops<br>1                                                                                                                          |    |

|     | clk           | B 0      |                                                                                                                                   | ٦  |

| D   | 1             | B 1      |                                                                                                                                   |    |

| Ď   | ± a           | S 0      | <u>0                                    </u>                                                                                      | 2  |

| Ď   | ±b            | S 7      | <u>7 X 31 X 55 X 79 X 103 X 127 X -105 X -81 X -57 X -33 X -9 X 15 X 39 X 63 X 87</u>                                             | X  |

| 1   | ±р            | S 0      | <u>(0)                                    </u>                                                                                    | 53 |

|     |               |          |                                                                                                                                   |    |

Figure 4.11 : Simulation Waveform for Modified Baugh-Wooley Multiplier

From results that have been discussed, it shows that the schematic design of Modified Baugh-Wooley Two's Complement Signed Multiplier is functioning correctly. D Flip-flop must be connected first to each inputs and outputs to provide a clock signal in order to check the speed performance. Pipelining approach applied to Modified Baugh-Wooley Two's Complement Signed Multiplier has not been able to produce the expected result yet, might be due to improper of placing pipeline register (D Flip-flop) in the schematic. This is because, some of the D Flip-flops must even be placed in data paths in which no work has been done.