#### REFERENCES

- [1] Marco Wiering, Intelligent Traffic Light Control, April 2003. http://www.ercim.org/publication/Ercim\_News/enw53/wiering.html

- [2] Thomas L.Floyd, (2006). 'Digital Fundamentals' 8<sup>th</sup> & 9<sup>th</sup> Edition, Pearson Education International.

- [3] De Schutter, B., De Moor B. Optimal Traffic Light Control for a Single Intersection International symposium on nonlinear theory and its applications (NOLTA '97) pages 1085-1088

- [4] Roozemond, D.A. Using intelligent agents for pro-active, real-time urban intersection control. European Journal of Operational Research 131(2001), 293-301.

- [5] Pappis, C.P. and Mamdani, E.H., (1977). A Fuzzy Logic Controller for a Traffic Junction, IEEE Transactions on Systems, Man and Cybernetics, pp 707-717.

- [6] Chiu, S., Adaptive traffic signal control using fuzzy logic.Proceedings of the IEEE Intelligent Vehicles Symposium, 98-107, 1992.

- [7] Hoyer, R., and Jumar, U., (1994). Fuzzy Control of Traffic Lights, Proc. IEEE International Conference on Fuzzy Systems, 1994, pp 1526-1531.

- [8] Janecek, J.J. and Zargham, M.R., (1995). A Fuzzy Logic Controller for a Traffic Signal, SPIE, Vol 2622, pp 687-691.

- [9] Chiang, K.T., Khalid, M., Yusof, R. 'Intelligent Traffic Lights Control by Fuzzy Logic', Malaysian Journal of Computer Science, Nov., 1995

- [10] Lin, Q., Kwan, B.W., and Tung, L.J., (1997). Traffic Signal Control Using Fuzzy Logic, Proc. IEEE International Conference on Fuzzy Systems 1997, pp 1644-1649.

- [11] Henry, J.J., Farges, J.L., Gallego, J.L. Neuro-fuzzy techniques for traffic control. Control Engineering Practice 6(1998), 755-761.

- [12] Trabia, M., Kaseko, M., Ande, M. Two-stage fuzzy logic controller for traffic signals. Transportation Research Part C7 (1999), 353-367.

- [13] Niittymäki, J., Nevala, R. Fuzzy adaptive traffic signal control principles and results. Proceedings of the IFSA World Congress and 20th NAFIPS International Conference. Vancouver, Canada, July 25-28, 2001, 2870-2875.

- [14] Wei, W., Zhang, Y., Bosco, Mbede, J., Zhang, Z., Song, J. Traffic signal control using fuzzy logic and MOGA. Proceedings of the 2001 IEEE International Conference on Systems, Man and Cybernetics. Tucson, USA, October 7-10, 2001, 1335-1340.

- [15] Weng Fook Lee, (1994). 'Verilog Coding for Logic Synthesis' 2<sup>nd</sup> Edition, John Wiley & Sons, Inc.USA.

- [16] University Program UP2 Education Kit User Guide, (2004) http://users.ece.gatech.edu/~hamblen/ALTERA/altera.htm.

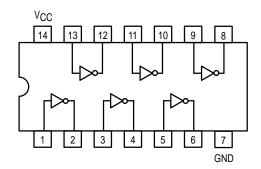

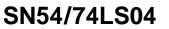

# **HEX INVERTER**

#### **GUARANTEED OPERATING RANGES**

| Symbol         | Parameter                           |          | Min         | Тур        | Max         | Unit |

|----------------|-------------------------------------|----------|-------------|------------|-------------|------|

| Vcc            | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| Т <sub>А</sub> | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| IOH            | Output Current — High               | 54, 74   |             |            | -0.4        | mA   |

| IOL            | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

## SN54/74LS04

|                 |                                            |        |     | Limits |      |      |                                          |                                                                                                |  |

|-----------------|--------------------------------------------|--------|-----|--------|------|------|------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Symbol          | Parameter                                  |        | Min | Тур    | Max  | Unit | Test Conditions                          |                                                                                                |  |

| VIH             | Input HIGH Voltage                         | _      | 2.0 |        |      | V    | Guaranteed Input<br>All Inputs           | HIGH Voltage for                                                                               |  |

|                 | Input LOW Voltage                          | 54     |     |        | 0.7  | V    | Guaranteed Input                         | LOW Voltage for                                                                                |  |

| VIL             | input LOW Voltage                          | 74     |     |        | 0.8  | v    | All Inputs                               |                                                                                                |  |

| VIK             | Input Clamp Diode Voltage                  |        |     | -0.65  | -1.5 | V    | $V_{CC} = MIN, I_{IN} =$                 | –18 mA                                                                                         |  |

| Maria           | Output HIGH Voltage                        | 54     | 2.5 | 3.5    |      | V    | V <sub>CC</sub> = MIN, I <sub>OH</sub> : | = MAX, V <sub>IN</sub> = V <sub>IH</sub>                                                       |  |

| VOH             | Culput mort voltage                        | 74     | 2.7 | 3.5    |      | V    | or VIL per Truth Table                   |                                                                                                |  |

| Vo              |                                            | 54, 74 |     | 0.25   | 0.4  | V    |                                          | V <sub>CC</sub> = V <sub>CC</sub> MIN,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> |  |

| VOL             | Output LOW Voltage                         | 74     |     | 0.35   | 0.5  | V    | I <sub>OL</sub> = 8.0 mA                 | per Truth Table                                                                                |  |

|                 |                                            |        |     |        | 20   | μΑ   | $V_{CC} = MAX, V_{IN}$                   | = 2.7 V                                                                                        |  |

| lΗ              | Input HIGH Current                         |        |     |        | 0.1  | mA   | $V_{CC} = MAX, V_{IN}$                   | = 7.0 V                                                                                        |  |

| ۱ <sub>IL</sub> | Input LOW Current                          |        |     |        | -0.4 | mA   | $V_{CC} = MAX, V_{IN}$                   | = 0.4 V                                                                                        |  |

| IOS             | Short Circuit Current (Note 1)             |        | -20 |        | -100 | mA   | V <sub>CC</sub> = MAX                    |                                                                                                |  |

| ICC             | Power Supply Current<br>Total, Output HIGH |        |     |        | 2.4  | mA   | V <sub>CC</sub> = MAX                    |                                                                                                |  |

|                 | Total, Output LOW                          |        |     |        | 6.6  |      |                                          |                                                                                                |  |

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

### AC CHARACTERISTICS (T<sub>A</sub> = $25^{\circ}$ C)

|                  |                                 |     | Limits |     |      |                         |

|------------------|---------------------------------|-----|--------|-----|------|-------------------------|

| Symbol           | Parameter                       | Min | Тур    | Max | Unit | Test Conditions         |

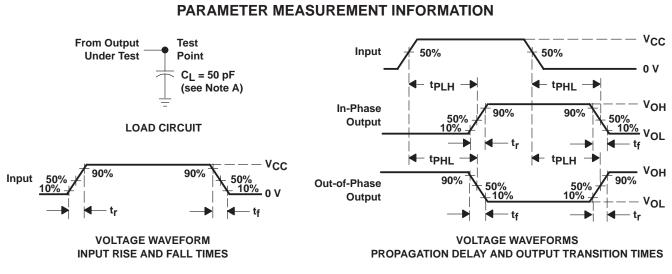

| <sup>t</sup> PLH | Turn-Off Delay, Input to Output |     | 9.0    | 15  | ns   | V <sub>CC</sub> = 5.0 V |

| <sup>t</sup> PHL | Turn-On Delay, Input to Output  |     | 10     | 15  | ns   | C <sub>L</sub> = 15 pF  |

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

FAIRCHILD

SEMICONDUCTOR

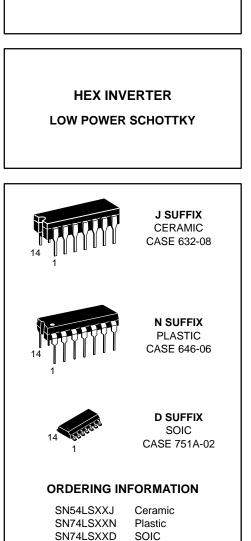

## DM74LS138 • DM74LS139 Decoder/Demultiplexer

### **General Description**

These Schottky-clamped circuits are designed to be used in high-performance memory-decoding or data-routing applications, requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When used with high-speed memories, the delay times of these decoders are usually less than the typical access time of the memory. This means that the effective system delay introduced by the decoder is negligible.

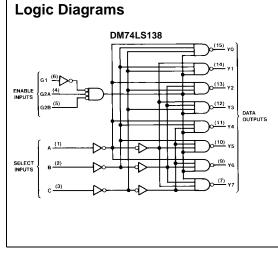

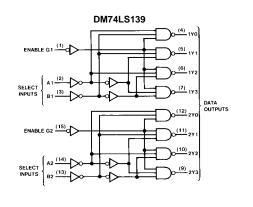

The DM74LS138 decodes one-of-eight lines, based upon the conditions at the three binary select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented with no external inverters, and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

The DM74LS139 comprises two separate two-line-to-fourline decoders in a single package. The active-low enable input can be used as a data line in demultiplexing applications.

All of these decoders/demultiplexers feature fully buffered inputs, presenting only one normalized load to its driving circuit. All inputs are clamped with high-performance Schottky diodes to suppress line-ringing and simplify system design.

#### Features

- Designed specifically for high speed: Memory decoders

- Data transmission systems

- DM74LS138 3-to-8-line decoders incorporates 3 enable inputs to simplify cascading and/or data reception

August 1986

Revised March 2000

- DM74LS139 contains two fully independent 2-to-4-line decoders/demultiplexers

- Schottky clamped for high performance

- Typical propagation delay (3 levels of logic)

DM74LS138 21 ns

DM74LS139 21 ns

- Typical power dissipation

DM74LS138 32 mW

DM74LS139 34 mW

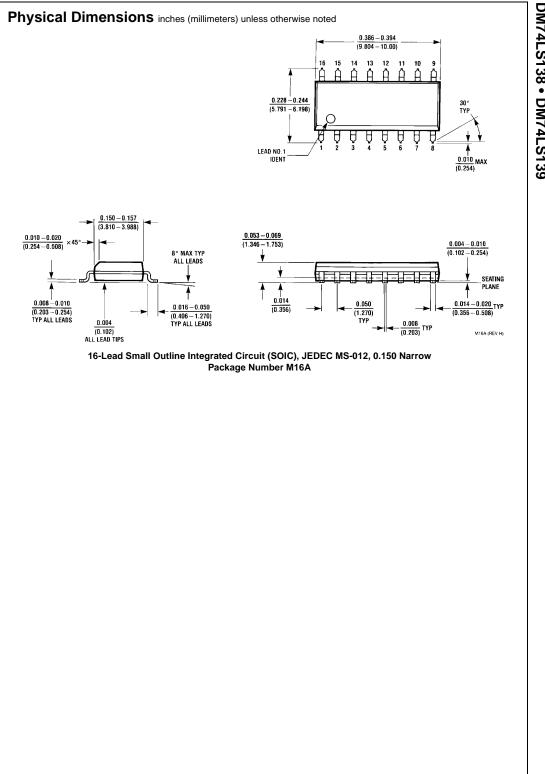

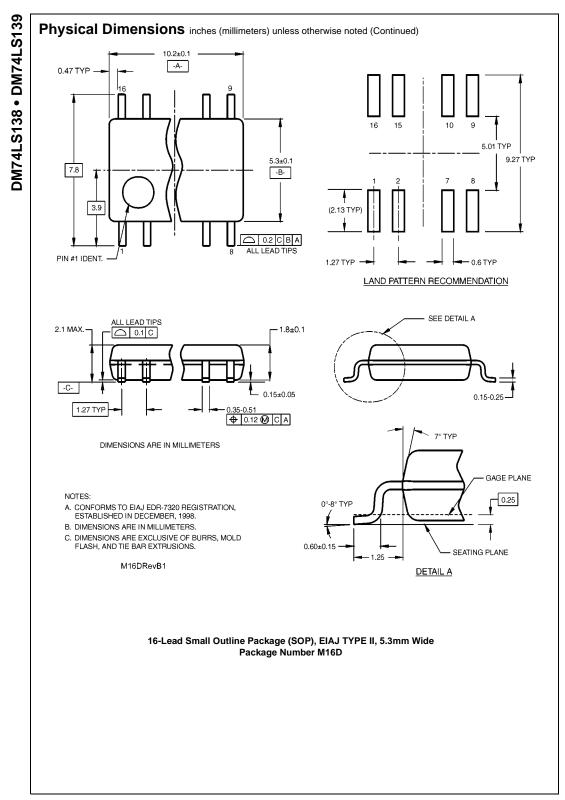

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

| DM74LS138M   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

| DM74LS138SJ  | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

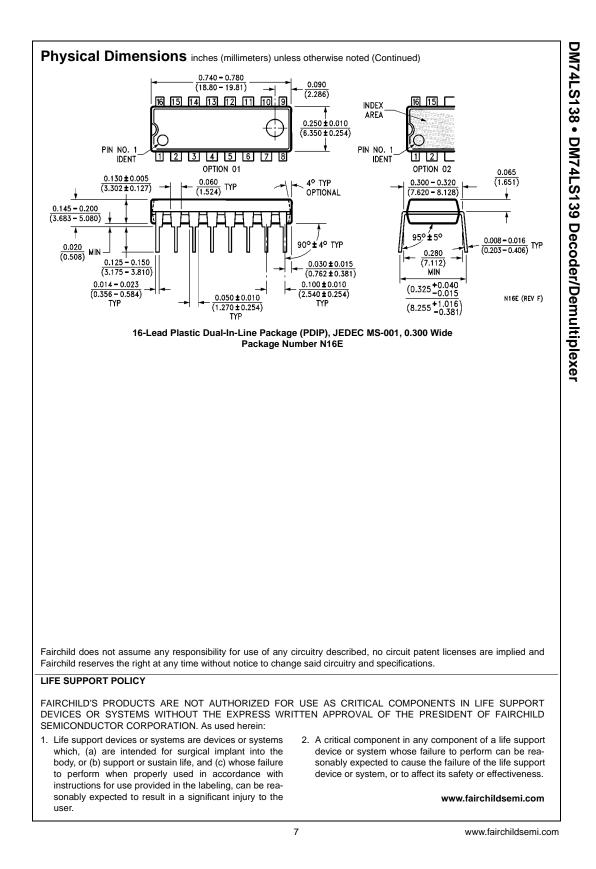

| DM74LS138N   | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

| DM74LS139M   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

| DM74LS139SJ  | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

| DM74LS139N   | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

## **Function Tables**

н

н

L

L

нн L н н н н н н L н

н н н н н н н н Н Н Т

|               | DM74LS138   |   |   |   |    |      |      |      |    |    |    |    |  |  |

|---------------|-------------|---|---|---|----|------|------|------|----|----|----|----|--|--|

|               | Inputs      |   |   |   |    | Outr | outs |      |    |    |    |    |  |  |

| Enable Select |             |   |   |   |    |      | սպ   | Juis |    |    |    |    |  |  |

| G1            | G2 (Note 1) | С | В | Α | YO | Y1   | Y2   | Y3   | Y4 | Y5 | Y6 | Y7 |  |  |

| Х             | Н           | Х | Х | Х | Н  | Н    | Н    | Н    | Н  | Н  | Н  | Н  |  |  |

| L             | Х           | Х | Х | Х | н  | н    | н    | н    | н  | н  | н  | н  |  |  |

| н             | L           | L | L | L | L  | н    | н    | н    | н  | н  | н  | н  |  |  |

| н             | L           | L | L | н | н  | L    | н    | н    | н  | н  | н  | н  |  |  |

| н             | L           | L | н | L | н  | н    | L    | н    | н  | н  | н  | н  |  |  |

| н             | L           | L | н | н | н  | н    | н    | L    | н  | н  | н  | н  |  |  |

| н             | L           | н | L | L | н  | н    | н    | н    | L  | н  | н  | н  |  |  |

| н             | L           | Н | L | н | н  | н    | н    | н    | н  | L  | н  | н  |  |  |

| D | M74L | S139 |

|---|------|------|

| In     | outs |     |         | Out | oute |    |  |

|--------|------|-----|---------|-----|------|----|--|

| Enable | Se   | ect | Outputs |     |      |    |  |

| G      | В    | Α   | Y0      | Y1  | Y2   | Y3 |  |

| Н      | Х    | Х   | Н       | Н   | Н    | Н  |  |

| L      | L    | L   | L       | н   | н    | н  |  |

| L      | L    | н   | н       | L   | н    | н  |  |

| L      | н    | L   | н       | н   | L    | н  |  |

| L      | н    | н   | н       | н   | н    | L  |  |

H = HIGH Level L = LOW Level X = Don't Care

Note 1: G2 = G2A + G2B

#### Absolute Maximum Ratings(Note 2)

| Supply Voltage                       | 7V                             |

|--------------------------------------|--------------------------------|

| Input Voltage                        | 7V                             |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$ |

| Storage Temperature Range            | -65°C to +150°C                |

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## DM74LS138 Recommended Operating Conditions

| Symbol | Parameter                      | Min  | Nom | Max  | Units |

|--------|--------------------------------|------|-----|------|-------|

| 'cc    | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| и      | HIGH Level Input Voltage       | 2    |     |      | V     |

| ΪL     | LOW Level Input Voltage        |      |     | 0.8  | V     |

| ЭН     | HIGH Level Output Current      |      |     | -0.4 | mA    |

| DL     | LOW Level Output Current       |      |     | 8    | mA    |

| A      | Free Air Operating Temperature | 0    |     | 70   | °C    |

### **DM74LS138 Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted) Тур Symbol Conditions Units Parameter Min Max (Note 3)  $V_{CC} = Min, I_I = -18 \text{ mA}$ Input Clamp Voltage -1.5 V VI HIGH Level Output Voltage  $V_{CC} = Min, I_{OH} = Max, V_{IL} = Max, V_{IH} = Min$ 2.7 3.4 V<sub>OH</sub> V  $V_{CC} = Min$ ,  $I_{OL} = Max$ ,  $V_{IL} = Max$ ,  $V_{IH} = Min$ V<sub>OL</sub> LOW Level 0.35 0.5 V Output Voltage  $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}$ 0.25 04  $V_{CC} = Max, V_I = 7V$ Input Current @ Max Input Voltage 0.1 mΑ h.  $V_{CC} = Max, V_I = 2.7V$ HIGH Level Input Current 20  $\mathsf{I}_{\mathsf{IH}}$ μΑ LOW Level Input Current  $V_{CC} = Max, V_I = 0.4V$ -0.36 mΑ Ι<sub>ΙL</sub> Short Circuit Output Current V<sub>CC</sub> = Max (Note 4) los -20 -100 mΑ V<sub>CC</sub> = Max (Note 5) Icc Supply Current 6.3 10 mΑ

Note 3: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 4: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 5: I<sub>CC</sub> is measured with all outputs enabled and OPEN.

### DM74LS138 Switching Characteristics

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

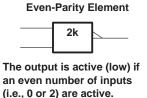

|                  |                                                    | From (Input)     | Levels   |                         | R <sub>L</sub> = | <b>2 k</b> Ω     |       |       |

|------------------|----------------------------------------------------|------------------|----------|-------------------------|------------------|------------------|-------|-------|

| Symbol           | Parameter                                          | To (Output)      | of Delay | <b>C</b> <sub>L</sub> = | 15 pF            | C <sub>L</sub> = | 50 pF | Units |

|                  |                                                    |                  |          | Min                     | Max              | Min              | Max   |       |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Select to Output | 2        |                         | 18               |                  | 27    | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Select to Output | 2        |                         | 27               |                  | 40    | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Select to Output | 3        |                         | 18               |                  | 27    | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Select to Output | 3        |                         | 27               |                  | 40    | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Enable to Output | 2        |                         | 18               |                  | 27    | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Enable to Output | 2        |                         | 24               |                  | 40    | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Enable to Output | 3        |                         | 18               |                  | 27    | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Enable to Output | 3        |                         | 28               |                  | 40    | ns    |

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| / <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| он              | HIGH Level Output Current      |      |     | -0.4 | mA    |

| OL              | LOW Level Output Current       |      |     | 8    | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

## DM74LS139 Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                                    | Min | Typ<br>(Note 6) | Max   | Units |

|-----------------|-----------------------------------|---------------------------------------------------------------|-----|-----------------|-------|-------|

| VI              | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$                          |     |                 | -1.5  | V     |

| V <sub>OH</sub> | HIGH Level<br>Output Voltage      | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max, V_{IH} = Min$ | 2.7 | 3.4             |       | V     |

| V <sub>OL</sub> | LOW Level<br>Output Voltage       | $V_{CC} = Min, I_{OL} = Max$<br>$V_{IL} = Max, V_{IH} = Min$  |     | 0.35            | 0.5   | V     |

|                 |                                   | $I_{OL} = 4 \text{ mA}, V_{CC} = Min$                         |     | 0.25            | 0.4   |       |

| l <sub>l</sub>  | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 7V$                                      |     |                 | 0.1   | mA    |

| I <sub>IH</sub> | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.7V$                                    |     |                 | 20    | μA    |

| IIL             | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.4V$                                    |     |                 | -0.36 | mA    |

| los             | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 7)                                | -20 |                 | -100  | mA    |

| I <sub>CC</sub> | Supply Current                    | V <sub>CC</sub> = Max (Note 8)                                |     | 6.8             | 11    | mA    |

Note 6: All typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

Note 7: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 8:  $I_{CC}$  is measured with all outputs enabled and OPEN.

## DM74LS139 Switching Characteristics

at  $V_{CC} = 5V$  and  $T_A = 25^\circ C$

|                  |                                                    | From (Input)     |                        |     |                       |     |       |

|------------------|----------------------------------------------------|------------------|------------------------|-----|-----------------------|-----|-------|

| Symbol           | Parameter                                          | To (Output)      | C <sub>L</sub> = 15 pl |     | 5 pF C <sub>L</sub> = |     | Units |

|                  |                                                    |                  | Min                    | Max | Min                   | Max |       |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Select to Output |                        | 18  |                       | 27  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Select to Output |                        | 27  |                       | 40  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Enable to Output |                        | 18  |                       | 27  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Enable to Output |                        | 24  |                       | 40  | ns    |

DM74LS138 • DM74LS139

#### **SDLS100**

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers and Flat Packages, and Plastic and Ceramic DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

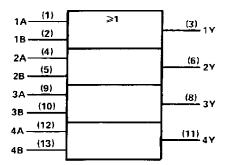

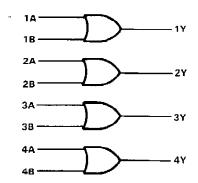

These devices contain four independent 2-input OR gates.

The SN5432, SN54LS32 and SN54S32 are characterized for operation over the full military range of -55°C to 125°C. The SN7432, SN74LS32 and SN74S32 are characterized for operation from 0°C to 70°C.

#### FUNCTION TABLE (each gate)

| INP | UTS | OUTPUT |

|-----|-----|--------|

| A   | B   | Ŷ      |

| н   | х   | н      |

| х   | н   | н      |

| L   | L   | L      |

logic symbol<sup>†</sup>

ì

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D. J. N. or W packages.

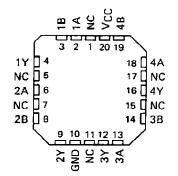

#### SN5432, SN54LS32, SN54S32, SN7432, SN74LS32, SN74S32 QUADRUPLE 2-INPUT POSITIVE-OR GATES DECEMBER 1983 - REVISED MARCH 1988

SN5432, SN54LS32, SN54S32 ... J OR W PACKAGE SN7432 . . . N PACKAGE SN74LS32, SN74S32 . . . D OR N PACKAGE (TOP VIEW)

| 1A []1<br>1B []2<br>1Y []3<br>2A []4<br>2B []5 | 14 VCC<br>13 4B<br>12 4A<br>11 4Y<br>10 3B |

|------------------------------------------------|--------------------------------------------|

| 2B 5<br>2Y 6                                   | _                                          |

|                                                | 8 3Y                                       |

SN54LS32, SN54S32 ... FK PACKAGE (TOP VIEW)

NC - No internal connection

logic diagram

positive logic

$$Y = A + B \text{ or } Y = \overline{A \cdot B}$$

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warrenty. Production processing does not necessarily include testing of all parameters.

### SN5432, SN54LS32, SN54S32, SN7432, SN74LS32, SN74S32 QUADRUPLE 2-INPUT POSITIVE-OR GATES

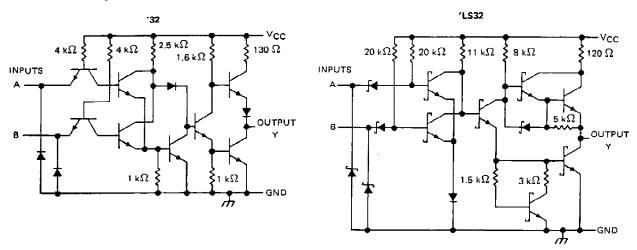

schematics (each gate)

Resistor values shown are nominal.

..

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                                    |             |

|---------------------------------------------------------------------|-------------|

| Input voltage: '32, 'S32                                            | 5.5 V       |

| ′L\$32                                                              |             |

| Operating free-air temperature: SN54'                               |             |

| SN74′                                                               | 0°C to 70°C |

| Storage temperature range                                           |             |

| NOTE 1: Voltage values are with respect to network ground terminal. |             |

#### recommended operating conditions

|      |                                |      | SN5432 |       |      | SN7432 |       |      |  |

|------|--------------------------------|------|--------|-------|------|--------|-------|------|--|

|      |                                | MIN  | NOM    | MAX   | MIN  | NOM    | MAX   | UNIT |  |

| Vcc  | Supply voltage                 | 4.5  | 5      | 5.5   | 4.75 | 5      | 5.25  | v    |  |

| ⊻ін  | Hgh-level input voltage        | 2    |        |       | 2    |        |       | V    |  |

| VIL  | Low-level imput voltage        |      |        | 0.8   |      |        | 0,8   | v    |  |

| юн   | High-level output current      |      |        | - 0.8 |      |        | ~ 0.8 | mA   |  |

| IOL. | Low-level output current       |      |        | 16    |      |        | 16    | mА   |  |

| TA   | Operating free-air temperature | - 55 |        | 125   | 0    |        | 70    | °C   |  |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| BARAMETER       |                        | TEST CONDIT            |                            |      | SN5432 |       | SN7432 |      |       | UNIT |

|-----------------|------------------------|------------------------|----------------------------|------|--------|-------|--------|------|-------|------|

| PARAMETER       |                        |                        |                            | MIN  | TYP‡   | ΜΑΧ   | MIN    | TYP‡ | MAX   | UNIT |

| <br>VIK         | VCC = MIN,             | li = - 12 mA           |                            |      |        | - 1.5 |        |      | - 1,5 | v    |

| V <sub>OH</sub> | V <sub>CC</sub> = MIN, | V <sub>IH</sub> ≈ 2 V, | I <sub>OH</sub> ≠ − 0.8 mA | 2.4  | 3.4    |       | 2.4    | 3.4  |       | V    |

| VOL             | V <sub>CC</sub> = MIN, | V <u>iL</u> ≈ 0.8 V,   | IOL = 16 mA                |      | 0,2    | 0.4   |        | 0.2  | 0.4   | V    |

| Ц               | V <sub>CC</sub> = MAX, | V1 = 5.5 V             |                            |      |        | 1     |        |      | 1     | mΑ   |

| _чн             | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 2.4 V |                            |      |        | 40    |        |      | 40    | μA   |

| հե              | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0.4 V |                            |      |        | 1.6   |        |      | - 1.6 | mΑ   |

| OS§             | VCC = MAX              |                        |                            | - 20 |        | - 55  | - 18   |      | - 55  | mА   |

| ІССН            | V <sub>CC</sub> = MAX, | See Note 2             |                            |      | 15     | 22    |        | 15   | 22    | mA   |

|                 | VCC * MAX,             | V1 = 0 V               |                            |      | 23     | 38    |        | 23   | 38    | mA   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

§ Not more than one output should be shorted at a time.

Ì

.

NOTE 2: One input at 4.5 V, all others at GND.

## switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C (see note 3)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT)                        | TEST CON                | DITIONS     | MIN | TYP | МАХ | UNIT |

|------------------|-----------------|---------------------------------------|-------------------------|-------------|-----|-----|-----|------|

| TPLH             | A or 8          | ×                                     | R <sub>L</sub> = 400 Ω, | C. = 15 = 5 |     | 10  | 15  | ris  |

| <sup>t</sup> PHL | 7018            | · · · · · · · · · · · · · · · · · · · | κ <u>ι</u> - 400 sz,    | CL = 15 pF  |     | 14  | 22  | ns   |

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

### SN54LS32, SN74LS32 QUADRUPLE 2 INPUT POSITIVE OR GATES

#### recommended operating conditions

|                       |                            |      | SN54LS32 |       |      | SN74LS32 |               |      |  |

|-----------------------|----------------------------|------|----------|-------|------|----------|---------------|------|--|

|                       |                            | MIN  | NOM      | MAX   | MIN  | NOM      | MAX           | UNIT |  |

| V <sub>CC</sub> Suppl | y voltage                  | 4.5  | 5        | 5.5   | 4.75 | 5        | 5.25          | V    |  |

| VIH Hgh-le            | evel input voltage         | 2    |          |       | 2    |          |               | V    |  |

| VIL Low-              | evel input voltage         |      |          | 0.7   |      |          | 0.8           | V    |  |

| OH High-I             | level output current       |      |          | - 0,4 |      |          | - <b>D</b> .4 | mĀ   |  |

| OL Low-I              | evel output current        |      |          | 4     |      |          | 8             | mΑ   |  |

| TA Opert              | ating free-air temperature | - 55 |          | 125   | 0    |          | 70            | °C   |  |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                        | 7567 00000             |                            |      | SN54LS | 32    |      | SN74LS | 32    |     |

|-----------|------------------------|------------------------|----------------------------|------|--------|-------|------|--------|-------|-----|

| PARAMETER |                        | TEST CONDITIONS †      |                            | MIN  | TYP\$  | MAX   | MIN  | TYP‡   | MAX   |     |

| Viĸ       | V <sub>CC</sub> - MIN, | l <sub>1</sub> = 18 mA |                            |      |        | - 1.5 |      |        | - 1.5 | v   |

| ∨он       | VCC = MIN,             | V <sub>IH</sub> = 2 V, | I <sub>OH</sub> = - 0.4 mA | 2.5  | 3.4    | •     | 2.7  | 3.4    |       | V   |

| 14        | VCC = MIN,             | VIL = MAX,             | 10L = 4 mA                 |      | 0.25   | 0.4   |      | 0.25   | 0.4   | v   |

| VOL       | V <sub>CC</sub> = MIN, | V <sub>IL</sub> = MAX, | IOL = 8 mA                 |      |        |       |      | 0.35   | 0.5   | ľ v |

| 1         | V <sub>CC</sub> - MAX, | V <sub>1</sub> = 7 V   |                            |      |        | 0.1   |      |        | 0.1   | mA  |

| -<br>IH   | VCC = MAX,             | V <sub>I</sub> = 2.7 V |                            |      | •      | 20    |      |        | 20    | μA  |

| IIL.      | V <sub>CC</sub> = MAX, | VI = 0.4 V             |                            |      |        | - 0.4 |      |        | - 0.4 | mA  |

| IOS§      | VCC = MAX              |                        |                            | - 20 |        | - 100 | - 20 |        | - 100 | mΑ  |

| Іссн      | V <sub>CC</sub> = MAX, | See Note 2             |                            |      | 3.1    | 6.2   |      | 3.1    | 6.2   | mA  |

| ICCL      | VCC = MAX,             | V <sub>1</sub> = 0 V   |                            | l    | 4.9    | 9.8   | I    | 4.9    | 9.8   | mΑ  |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

f All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ . § Not more than one output should be shorted at a time and the duration of the short-circuit should not exceed one second. NOTE 2: One input at 4.5 V, all others at GND.

#### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 3)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST COM              | MIN        | түр | МАХ | UNIT |    |

|------------------|-----------------|----------------|-----------------------|------------|-----|-----|------|----|

| tPLH             | 1 az 0          | V              | <b>D</b> 010          | 0 - 15 -   |     | 14  | 22   | пs |

| <sup>t</sup> PHL | A or B          | T              | $R_{L} = 2 k \Omega,$ | CL = 15 pF |     | 14  | 22   | ns |

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

#### recommended operating conditions

|                 |                                |      | SN5453 | 2   |      | 2   | UNIT |      |

|-----------------|--------------------------------|------|--------|-----|------|-----|------|------|

|                 |                                | MIN  | NOM    | MAX | MIN  | NOM | MAX  | UNIT |

| Vcc             | Supply voltage                 | 4.5  | 5      | 5.5 | 4.75 | 5   | 5.25 | v    |

| Viн             | High-level input voltage       | 2    |        |     | 2    |     |      | v    |

| VIL             | Low-level input voltage        |      |        | 0.8 |      |     | 0.8  | v    |

| юн              | High-level output current      |      |        | 1   |      |     | - 1  | mΑ   |

| <sup>I</sup> OL | Low-level output current       |      |        | 20  |      |     | 20   | mΑ   |

| TA              | Operating free-air temperature | - 55 |        | 125 | 0    |     | 70   | °C   |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           | TEST CONDITIONS <sup>†</sup> |                          |              | SN54S3 | 2     |               | 1.0017 |       |       |      |

|-----------|------------------------------|--------------------------|--------------|--------|-------|---------------|--------|-------|-------|------|

| PARAMETER |                              |                          |              | MIN    | TYP ‡ | MAX           | MIN    | TYP # | MAX   | UNIT |

| VIK       | VCC = MIN,                   | lj = — 18 mA             |              |        |       | - 1.2         |        |       | - 1.2 | V    |

| ∨он       | V <sub>CC</sub> = MIN,       | V <sub>IH</sub> = 2 V,   | 10H = - 1 mA | 2.5    | 3.4   |               | 2.7    | 3.4   |       | V    |

| VoL       | VCC = MIN,                   | V <sub>IL</sub> = 0.8 V, | IOL = 20 mA  |        |       | 0.5           |        |       | 0.5   | V    |

| 4         | V <sub>CC</sub> = MAX,       | V <sub>1</sub> = 5.5 V   |              |        |       | 1             |        |       | 1     | mA   |

| Чн        | VCC = MAX,                   | V  = 2.7 V               |              |        |       | 50            |        |       | 50    | μA   |

| ΊL        | V <sub>CC</sub> = MAX,       | Vi = 0.5 V               |              |        |       | - 2           |        |       | - 2   | MA   |

| los§      | V <sub>CC</sub> = MAX        |                          |              | - 40   |       | — 1 <b>00</b> | - 40   |       | - 100 | mA   |

| Іссн      | V <sub>CC</sub> = MAX,       | See Note 2               |              |        | 18    | 32            |        | 18    | 32    | mA   |

| ICCL      | VCC = MAX,                   | V1 = 0 V                 |              |        | - 38  | 68            |        | - 38  | 68    | mA   |

2

-

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. ‡ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . § Not more than one output should be shorted at a time and the duration of the short-circuit should not exceed one second. NOTE 2: One input at 4.5 V, all others at GND.

switching characteristics, VCC = 5 V, TA =  $25^{\circ}$ C (see note 3)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CON                |                        | MIN TY | P MAX | UNIT |

|------------------|-----------------|----------------|-------------------------|------------------------|--------|-------|------|

| tPLH             | A or B          | v              | <b>D</b> = 200 O        | C <sub>I</sub> = 15 pF |        | 4 7   | ns   |

| tPHL             | A OF B          | 1              | RL ≈ 280 Ω,             |                        |        | 4 7   | ns   |

| tPLH             | A or 8          | v              | R <sub>I</sub> = 280 Ω, | CI = 50 pF             |        | 5     | пs   |

| <sup>t</sup> ₽HL |                 |                | ni <b>10</b> 0 02,      |                        |        | 5     | ns   |

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

TEXAS INSTRUMENTS www.ti.com

6-Dec-2006

### **PACKAGING INFORMATION**

| Orderable Device                      | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|---------------------------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| 5962-9557401QCA                       | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| 5962-9557401QDA                       | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| 5962-9557401QDA                       | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| JM38510/30501B2A                      | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| JM38510/30501B2A                      | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| JM38510/30501BCA                      | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| JM38510/30501BCA                      | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| JM38510/30501BDA                      | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| JM38510/30501BDA                      | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| JM38510/30501SCA                      | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| JM38510/30501SCA                      | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| JM38510/30501SDA                      | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| JM38510/30501SDA                      | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SN5432J                               | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN5432J                               | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN54LS32J                             | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN54LS32J                             | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN54S32J                              | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN54S32J                              | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SN7432N                               | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN7432N                               | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN7432N3                              | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| SN7432N3                              | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| SN7432NE4                             | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN7432NE4                             | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN74LS32D                             | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32D                             | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DBR                           | ACTIVE                | SSOP            | DB                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DBR                           | ACTIVE                | SSOP            | DB                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DBRE4                         | ACTIVE                | SSOP            | DB                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DBRE4                         | ACTIVE                | SSOP            | DB                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DE4                           | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DE4                           | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74LS32DG4                           | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS &             | CU NIPDAU        | Level-1-260C-UNLIM           |

| · · · · · · · · · · · · · · · · · · · |                       |                 |                    |      |                |                           |                  |                              |

## PACKAGE OPTION ADDENDUM

6-Dec-2006

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|----------------------------|

|                  |                       |                 |                    |      |                | no Sb/Br)                 |                  |                            |

| SN74LS32DG4      | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DR       | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DRE4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DRE4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32DRG4     | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN         |

| SN74LS32J        | OBSOLETE              | CDIP            | J                  | 14   |                | TBD                       | Call TI          | Call TI                    |

| SN74LS32J        | OBSOLETE              | CDIP            | J                  | 14   |                | TBD                       | Call TI          | Call TI                    |

| SN74LS32N        | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type         |

| SN74LS32N        | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type         |

| SN74LS32N3       | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                    |

| SN74LS32N3       | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                    |

| SN74LS32NE4      | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type         |

| SN74LS32NE4      | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type         |

| SN74LS32NSR      | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74LS32NSR      | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74LS32NSRG4    | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74LS32NSRG4    | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32D         | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32D         | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DE4       | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DE4       | ACTIVE                | SOIC            | D                  | 14   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DR        | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DR        | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DRE4      | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

| SN74S32DRE4      | ACTIVE                | SOIC            | D                  | 14   | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLI          |

## PACKAGE OPTION ADDENDUM

6-Dec-2006

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| SN74S32N         | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN74S32N         | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN74S32N3        | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| SN74S32N3        | OBSOLETE              | PDIP            | Ν                  | 14   |                | TBD                       | Call TI          | Call TI                      |

| SN74S32NE4       | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN74S32NE4       | ACTIVE                | PDIP            | Ν                  | 14   | 25             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type           |

| SN74S32NSR       | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74S32NSR       | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN74S32NSRE4     | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN           |

| SN74S32NSRE4     | ACTIVE                | SO              | NS                 | 14   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIN           |

| SNJ5432J         | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ5432J         | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ5432W         | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SNJ5432W         | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SNJ54LS32FK      | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| SNJ54LS32FK      | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| SNJ54LS32J       | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ54LS32J       | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ54LS32W       | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SNJ54LS32W       | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SNJ54S32FK       | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| SNJ54S32FK       | ACTIVE                | LCCC            | FK                 | 20   | 1              | TBD                       | POST-PLATE       | N / A for Pkg Type           |

| SNJ54S32J        | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ54S32J        | ACTIVE                | CDIP            | J                  | 14   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| SNJ54S32W        | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

| SNJ54S32W        | ACTIVE                | CFP             | W                  | 14   | 1              | TBD                       | A42              | N / A for Pkg Type           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

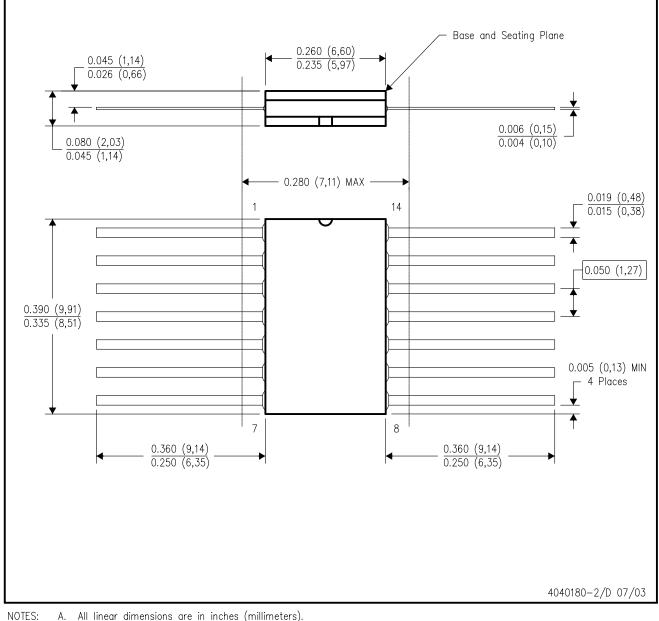

J (R-GDIP-T\*\*) 14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

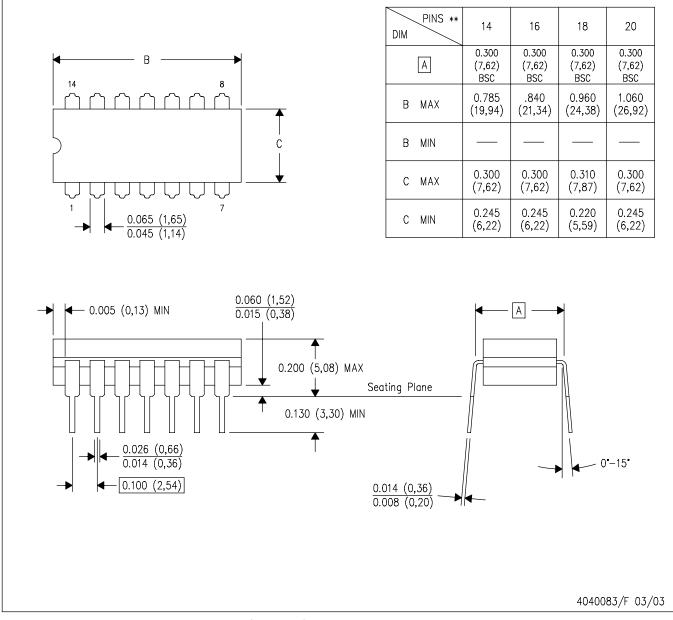

W (R-GDFP-F14)

CERAMIC DUAL FLATPACK

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL STD 1835 GDFP1-F14 and JEDEC MO-092AB

MLCC006B - OCTOBER 1996

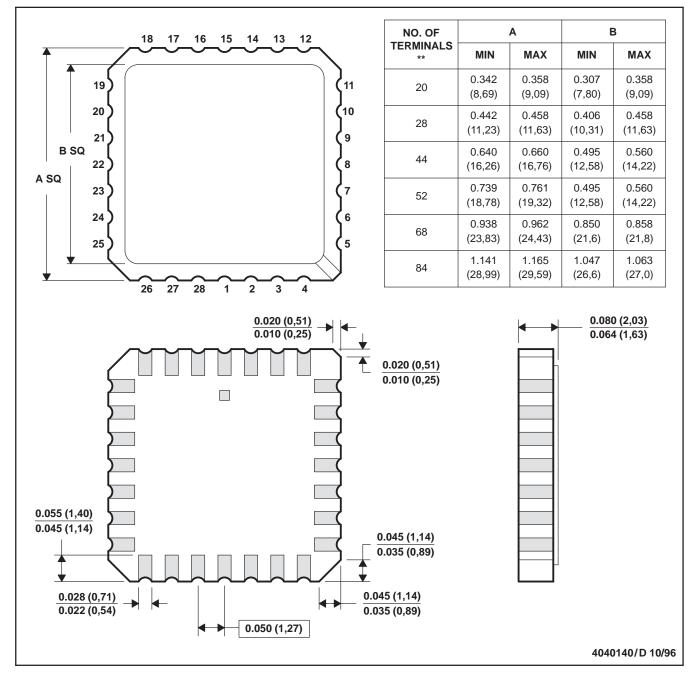

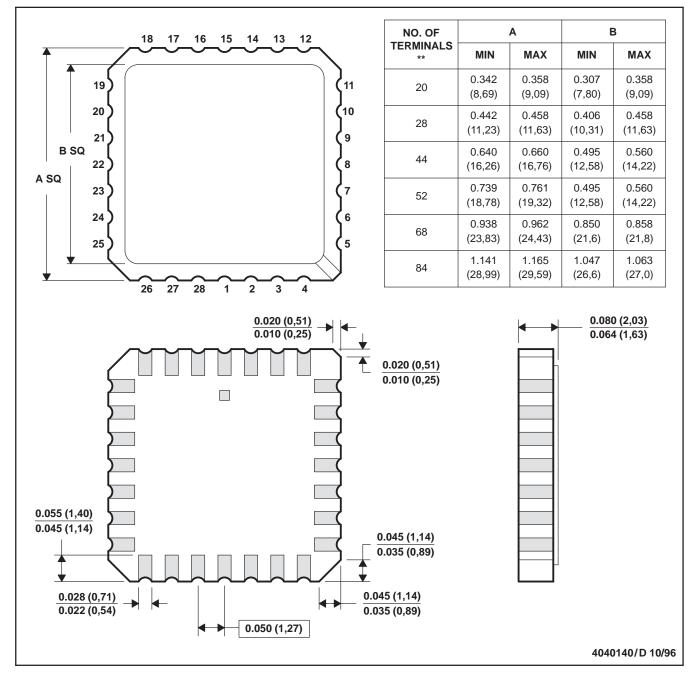

### FK (S-CQCC-N\*\*)

#### LEADLESS CERAMIC CHIP CARRIER

28 TERMINAL SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within JEDEC MS-004

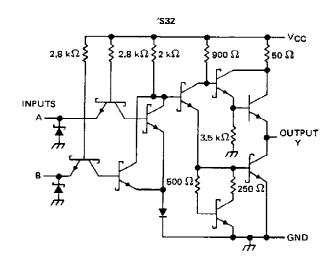

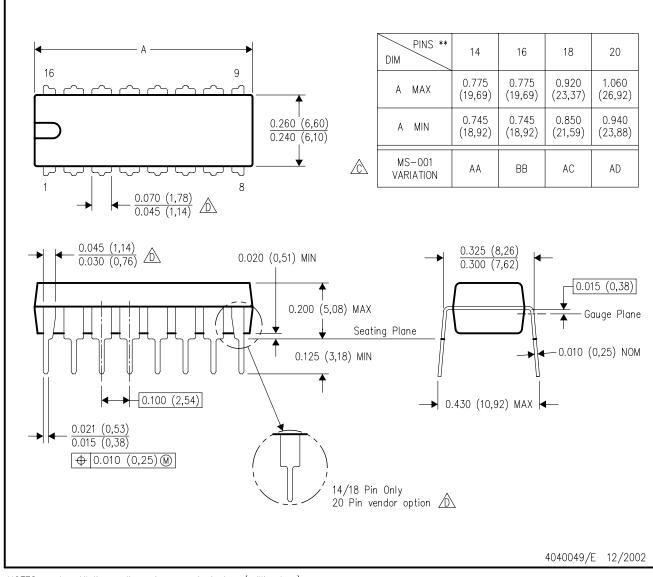

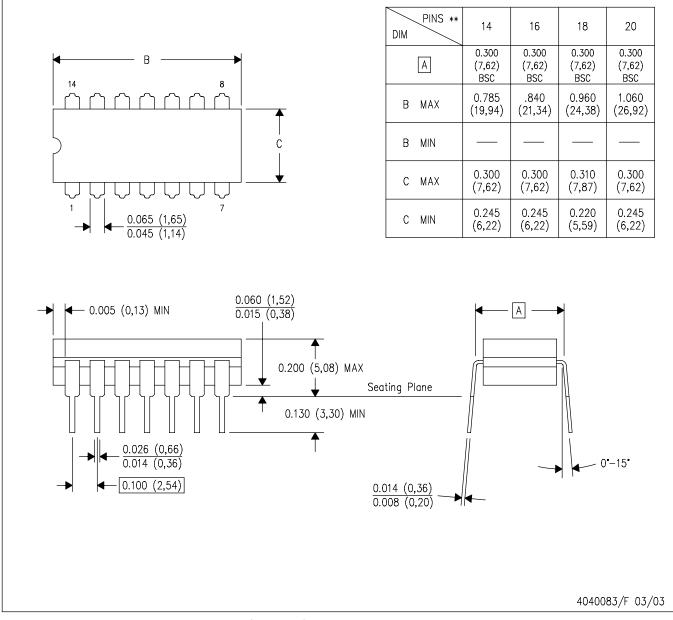

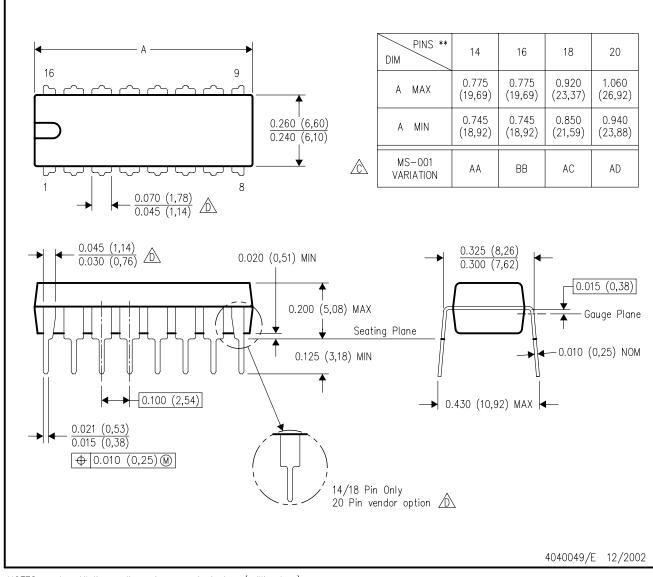

## N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

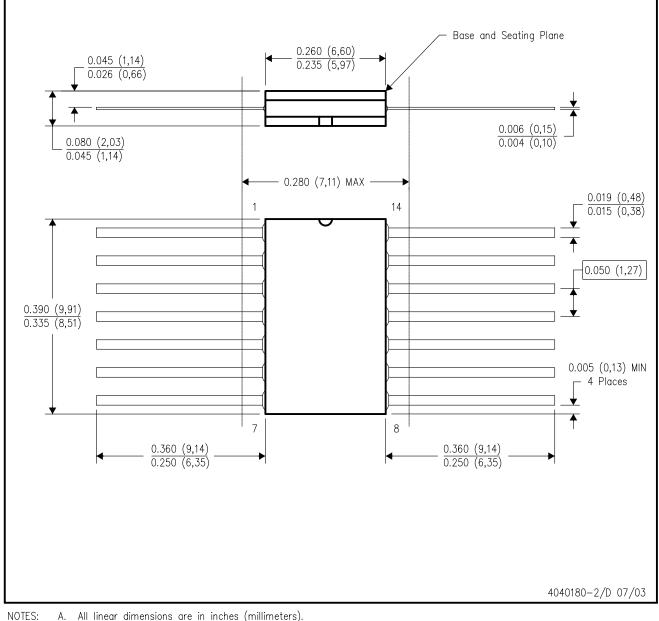

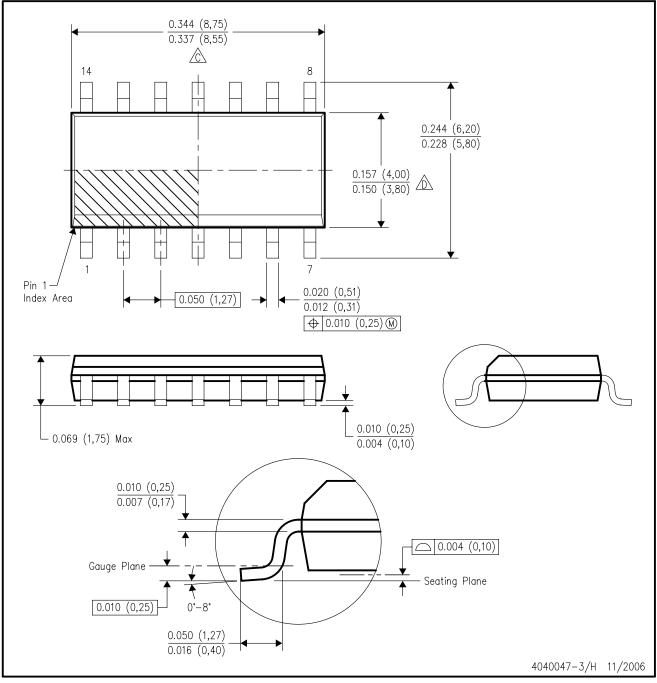

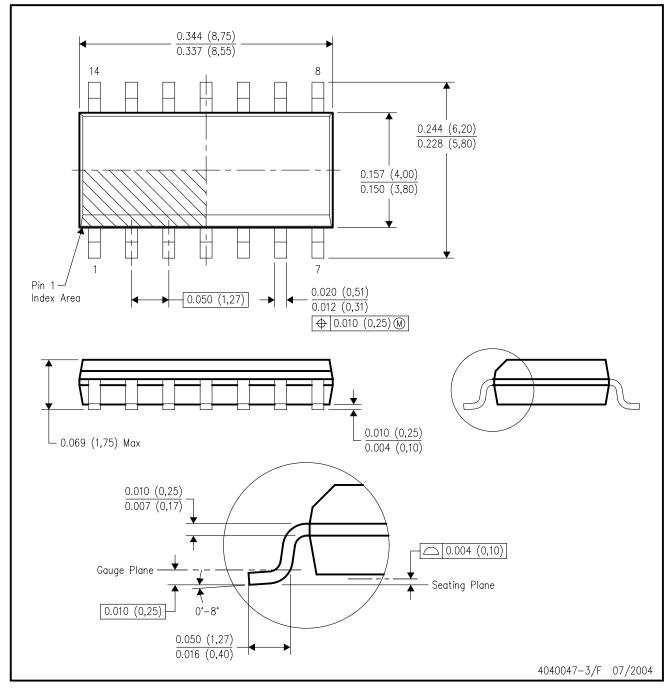

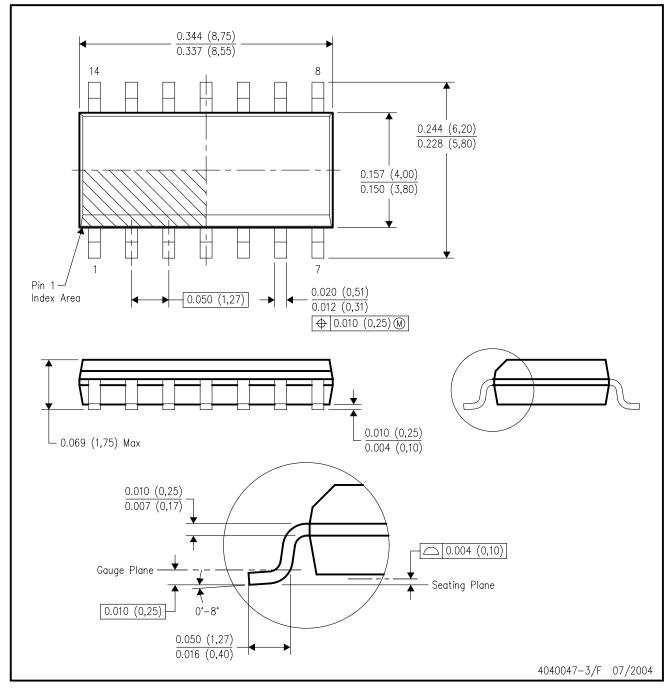

D (R-PDSO-G14)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

E. Reference JEDEC MS-012 variation AB.

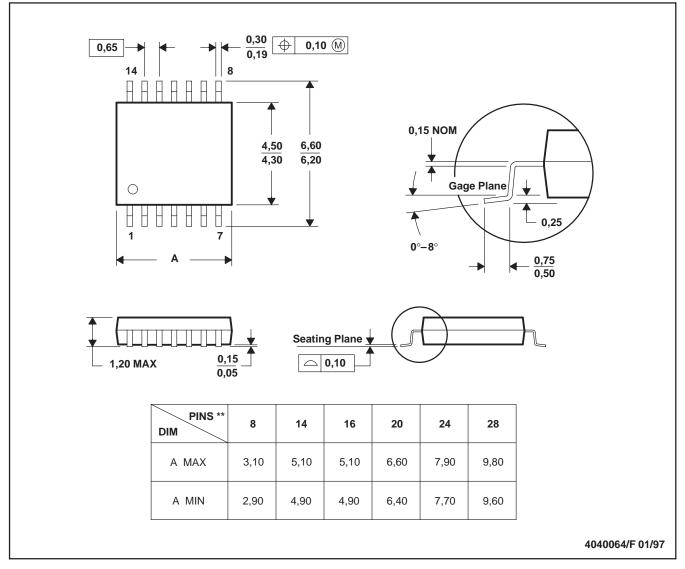

### MECHANICAL DATA

### PLASTIC SMALL-OUTLINE PACKAGE

#### 0,51 0,35 ⊕0,25⊛ 1,27 8 14 0,15 NOM 5,60 8,20 5,00 7,40 $\bigcirc$ Gage Plane ₽ 0,25 7 1 1,05 0,55 0-10 Δ 0,15 0,05 Seating Plane — 2,00 MAX 0,10PINS \*\* 14 16 20 24 DIM 10,50 10,50 12,90 15,30 A MAX A MIN 9,90 9,90 12,30 14,70 4040062/C 03/03

NOTES: A. All linear dimensions are in millimeters.

NS (R-PDSO-G\*\*)

**14-PINS SHOWN**

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15.

## **MECHANICAL DATA**

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

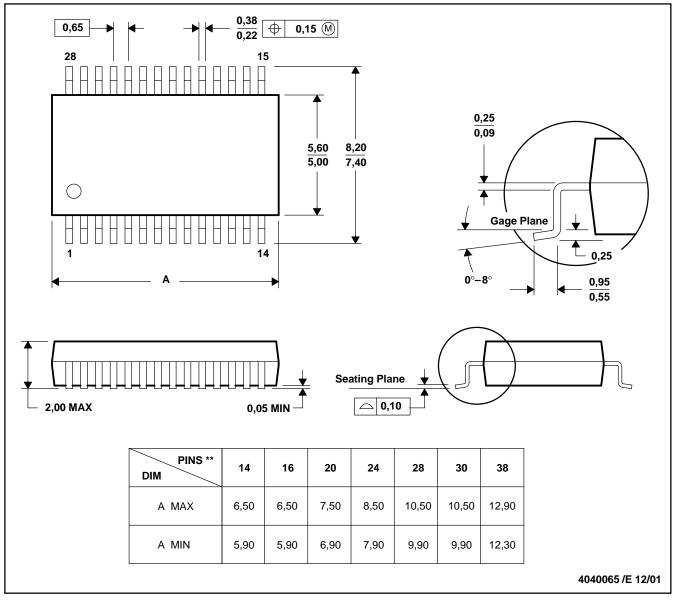

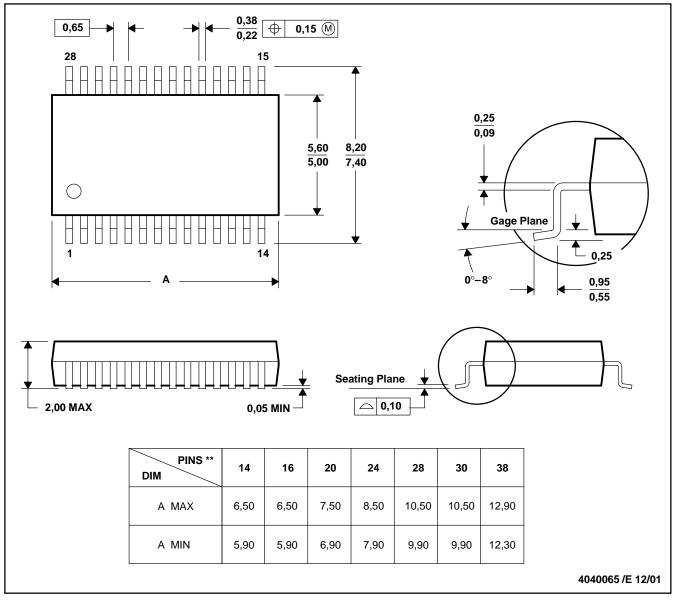

## DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated

# LM555 Timer General Description

The LM555 is a highly stable device for generating accurate time delays or oscillation. Additional terminals are provided for triggering or resetting if desired. In the time delay mode of operation, the time is precisely controlled by one external resistor and capacitor. For astable operation as an oscillator, the free running frequency and duty cycle are accurately controlled with two external resistors and one capacitor. The circuit may be triggered and reset on falling waveforms, and the output circuit can source or sink up to 200mA or drive TTL circuits.

### **Features**

- Direct replacement for SE555/NE555

- Timing from microseconds through hours

- Operates in both astable and monostable modes

- Adjustable duty cycle

- Output can source or sink 200 mA

- Output and supply TTL compatible

- Temperature stability better than 0.005% per °C

- Normally on and normally off output

- Available in 8-pin MSOP package

## Applications

- Precision timing

- Pulse generation

- Sequential timing

- Time delay generation

- Pulse width modulation

- Pulse position modulation

- Linear ramp generator

July 2006

LM555

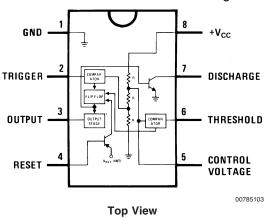

## **Connection Diagram**

Dual-In-Line, Small Outline and Molded Mini Small Outline Packages

## **Ordering Information**

| Package    | Part Number | Package Marking | Media Transport          | NSC Drawing |

|------------|-------------|-----------------|--------------------------|-------------|

| 8-Pin SOIC | LM555CM     | LM555CM         | Rails                    | M08A        |

|            | LM555CMX    | LM555CM         | 2.5k Units Tape and Reel | IVIUOA      |

| 8-Pin MSOP | LM555CMM    | Z55             | 1k Units Tape and Reel   | MUA08A      |

|            | LM555CMMX   | Z55             | 3.5k Units Tape and Reel | MUAUGA      |

| 8-Pin MDIP | LM555CN     | LM555CN         | Rails                    | N08E        |

## Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage               | +18V            |

|------------------------------|-----------------|

| Power Dissipation (Note 3)   |                 |

| LM555CM, LM555CN             | 1180 mW         |

| LM555CMM                     | 613 mW          |

| Operating Temperature Ranges |                 |

| LM555C                       | 0°C to +70°C    |

| Storage Temperature Range    | –65°C to +150°C |

| Soldering Information                          |        |

|------------------------------------------------|--------|

| Dual-In-Line Package                           |        |

| Soldering (10 Seconds)                         | 260°C  |

| Small Outline Packages                         |        |

| (SOIC and MSOP)                                |        |

| Vapor Phase (60 Seconds)                       | 215°C  |

| Infrared (15 Seconds)                          | 220°C  |

| See AN-450 "Surface Mounting Methods and Their | Effect |

|                                                |        |

on Product Reliability" for other methods of soldering surface mount devices.

## Electrical Characteristics (Notes 1, 2)

$(T_A = 25^{\circ}C, V_{CC} = +5V \text{ to } +15V, \text{ unless othewise specified})$

| Parameter                 | Conditions                            |     | Limits |      | Units             |  |

|---------------------------|---------------------------------------|-----|--------|------|-------------------|--|

|                           |                                       |     | LM555C |      |                   |  |

|                           |                                       | Min | Тур    | Max  | ]                 |  |

| Supply Voltage            |                                       | 4.5 |        | 16   | V                 |  |

| Supply Current            | $V_{\rm CC} = 5V, R_{\rm L} = \infty$ |     | 3      | 6    |                   |  |

|                           | $V_{CC} = 15V, R_{L} = \infty$        |     | 10     | 15   | mA                |  |

|                           | (Low State) (Note 4)                  |     |        |      |                   |  |

| Timing Error, Monostable  |                                       |     |        |      |                   |  |

| Initial Accuracy          |                                       |     | 1      |      | %                 |  |

| Drift with Temperature    | $R_A = 1k \text{ to } 100k\Omega,$    |     | 50     |      | ppm/°C            |  |

|                           | $C = 0.1 \mu F$ , (Note 5)            |     |        |      |                   |  |

| Accuracy over Temperature |                                       |     | 1.5    |      | %                 |  |

| Drift with Supply         |                                       |     | 0.1    |      | %/V               |  |

| Timing Error, Astable     |                                       |     |        |      |                   |  |

| Initial Accuracy          |                                       |     | 2.25   |      | %                 |  |

| Drift with Temperature    | $R_A$ , $R_B = 1k$ to $100k\Omega$ ,  |     | 150    |      | ppm/°C            |  |

|                           | C = 0.1µF, (Note 5)                   |     |        |      |                   |  |

| Accuracy over Temperature |                                       |     | 3.0    |      | %                 |  |

| Drift with Supply         |                                       |     | 0.30   |      | %/V               |  |

| Threshold Voltage         |                                       |     | 0.667  |      | x V <sub>CC</sub> |  |

| Trigger Voltage           | $V_{\rm CC} = 15V$                    |     | 5      |      | V                 |  |

|                           | $V_{\rm CC} = 5V$                     |     | 1.67   |      | V                 |  |

| Trigger Current           |                                       |     | 0.5    | 0.9  | μA                |  |

| Reset Voltage             |                                       | 0.4 | 0.5    | 1    | V                 |  |

| Reset Current             |                                       |     | 0.1    | 0.4  | mA                |  |

| Threshold Current         | (Note 6)                              |     | 0.1    | 0.25 | μA                |  |

| Control Voltage Level     | $V_{\rm CC} = 15V$                    | 9   | 10     | 11   | v                 |  |

|                           | $V_{\rm CC} = 5V$                     | 2.6 | 3.33   | 4    | v v               |  |

| Pin 7 Leakage Output High |                                       |     | 1      | 100  | nA                |  |

| Pin 7 Sat (Note 7)        |                                       |     |        |      |                   |  |

| Output Low                | $V_{CC} = 15V, I_7 = 15mA$            |     | 180    |      | mV                |  |

| Output Low                | $V_{\rm CC} = 4.5 V, I_7 = 4.5 mA$    |     | 80     | 200  | mV                |  |

LM555

## Electrical Characteristics (Notes 1, 2) (Continued)

$(T_A = 25^{\circ}C, V_{CC} = +5V \text{ to } +15V, \text{ unless othewise specified})$

| Parameter                  | Conditions                                         |       | Limits |      |    |  |  |

|----------------------------|----------------------------------------------------|-------|--------|------|----|--|--|

|                            |                                                    |       | LM555C |      |    |  |  |

|                            |                                                    | Min   | Тур    | Мах  |    |  |  |

| Output Voltage Drop (Low)  | V <sub>CC</sub> = 15V                              |       |        |      |    |  |  |

|                            | I <sub>SINK</sub> = 10mA                           |       | 0.1    | 0.25 | V  |  |  |

|                            | I <sub>SINK</sub> = 50mA                           |       | 0.4    | 0.75 | V  |  |  |

|                            | I <sub>SINK</sub> = 100mA                          |       | 2      | 2.5  | V  |  |  |

|                            | I <sub>SINK</sub> = 200mA                          |       | 2.5    |      | V  |  |  |

|                            | $V_{CC} = 5V$                                      |       |        |      |    |  |  |

|                            | I <sub>SINK</sub> = 8mA                            |       |        |      | V  |  |  |

|                            | I <sub>SINK</sub> = 5mA                            |       | 0.25   | 0.35 | V  |  |  |

| Output Voltage Drop (High) | $I_{SOURCE} = 200 \text{mA}, V_{CC} = 15 \text{V}$ |       | 12.5   |      | V  |  |  |